# Simulator for PowerPC

Release 09.2024

| TRACE32 Online Help                |                                                   |    |

|------------------------------------|---------------------------------------------------|----|

| TRACE32 Directory                  |                                                   |    |

| TRACE32 Index                      |                                                   |    |

| TRACE32 Documents                  |                                                   | Þ  |

| TRACE32 Instruction Set Simulators |                                                   | Þ  |

| Simulator for PowerPC              |                                                   | 1  |

| TRACE32 Simulator License          |                                                   | 5  |

|                                    |                                                   | 6  |

|                                    |                                                   |    |

| •                                  |                                                   | 8  |

| Troubleshooting                    |                                                   | 8  |

| FAQ                                |                                                   | 8  |

| Memory Classes                     |                                                   | 9  |

| Simulated Registers                |                                                   | 10 |

| CPU specific SYStem Commands       |                                                   | 12 |

| SYStem.CPU                         | Select CPU type                                   | 12 |

| SYStem.MemAccess                   | Select run-time memory access method              | 12 |

| SYStem.Mode                        | Establish the communication with the simulator    | 12 |

| SYStem.Option.Address32            | Define address format display                     | 13 |

| SYStem.Option.DisMode              | Simulator operation mode                          | 14 |

| SYStem.Option.DUALPORT             | Run-time memory access for all windows            | 14 |

| SYStem.Option.IMASKASM             | Disable interrupts while single stepping          | 15 |

| SYStem.Option.IMASKHLL             | Disable interrupts while HLL single stepping      | 15 |

| SYStem.Option.MMUSPACES            | Separate address spaces by space IDs              | 16 |

| SYStem.Option.MACHINESPACES        | Address extension for guest OSes                  | 17 |

| SYStem.Option.NOTRAP               | Use alternative software breakpoint instruction   | 17 |

| SYStem.Option.OVERLAY              | Enable overlay support                            | 18 |

| SYStem.Option.REALTIME             | Stall the simulator if faster than real processor | 18 |

| SYStem.Option.TranslationSPACE     | Identify user and hypervisor modes                | 19 |

| SYStem.Option.ZoneSPACES           | Enable symbol management for zones                | 20 |

| CPU specific MMU Commands          |                                                   | 23 |

| MMU.DUMP                           | Page wise display of MMU translation table        | 23 |

| MMU.FORMAT                         | Define MMU table structure                        | 25 |

| MMU.List                           | Compact display of MMU translation table          | 31 |

| MMU.SCAN                           | Load MMU table from CPU                           | 33 |

| TrOnchip Commands                  |                                                   | 35 |

TrOnchip.state TrOnchip.RESet

# Version 05-Oct-2024

|              | it View                                        | Var Brea                                          | k Run            | CPU Mis       | Trace Pro            | obe Perf            | Cov PPC40x              | Window   | Help      |            |                                            |        |

|--------------|------------------------------------------------|---------------------------------------------------|------------------|---------------|----------------------|---------------------|-------------------------|----------|-----------|------------|--------------------------------------------|--------|

| 1 1          | 14 I +                                         | 4 €                                               | ► II             | 2 ? •         | ?   💿   📰            | 101                 | <b>\$7</b> 65 65   1    | 🖲 🧎 🔑    |           |            |                                            |        |

| 3 p., r ;    | st.auto                                        |                                                   |                  |               |                      |                     |                         |          |           |            |                                            |        |

|              |                                                | Ouer I                                            | Diverse          | . Deturn      | d lla                | <b>b</b> .Co.       | II Break                | NºI Mada |           | Finds      |                                            |        |

| Ste<br>ade   |                                                | code                                              |                  | Return        |                      | ► Go                | Comment                 | Mode     | 5 t. 🥆    | Find:      | diabp4.c                                   | 1      |

|              |                                                | 39600001<br>7D6CF9AE                              |                  | li<br>stbx    | r11,                 | 0x1<br>r12.r31      | ; r11,1<br>; r11,r12    | -        |           |            |                                            | ^      |

| ASP:FI       | FF011F0                                        | 3BFF0001                                          |                  | addi          | r31,                 | r31,0x1             | ; i,i,1                 | , 1      |           |            |                                            |        |

| ASP:FI       | FF011F4                                        | 4BFFFFE4                                          | _                | b             | 0xFF                 | F011D8              |                         | _        | _         | _          |                                            | _      |

| ASD • EI     | 623                                            | 3BE00000                                          | for ( i          | = 0 ; i<br>li | <= SIZE ; *<br>r31,0 |                     | ; i.0                   |          |           |            |                                            |        |

|              |                                                |                                                   |                  |               |                      |                     | , 1,0                   |          |           |            |                                            |        |

|              |                                                | 2C1F0012                                          |                  | cmpw          |                      | 0x12                | ; i,18                  |          |           |            |                                            |        |

| ASP:FI       | FF01200                                        | 41810050                                          | 1                | bgt           | 0xFF                 | F01250              | ; 0xFFF01               | 250 (-)  |           |            |                                            |        |

|              | 625                                            |                                                   |                  |               | gs[i])               | 005                 | 10 . 15                 |          |           |            |                                            |        |

|              |                                                | 3D80FFF1<br>398CC468                              |                  | lis<br>subi   |                      | -0x0F<br>r12,0x3B98 | ; r12,-15<br>8 ; r12,r1 | 12,15256 |           |            |                                            |        |

|              |                                                | 7D8CF8AE                                          |                  | 1bzx<br>cmpw  | r12,                 | r12,r31             | ; r12,r12<br>; r12,0    |          |           |            |                                            |        |

|              |                                                | 41820034                                          |                  | beq           |                      | F01248              | ; 0xFFF01               | 248 (-)  |           |            |                                            | ~      |

|              |                                                | <                                                 |                  |               |                      |                     |                         |          |           |            |                                            | >      |

| 2 p          |                                                | cals /Caller                                      |                  |               |                      |                     | B::Var.W                |          |           |            |                                            | • 33   |

|              |                                                | -                                                 | _                |               |                      |                     | D::var.vv               | atch     |           |            |                                            |        |

|              | p 🤍 🖓 I                                        | Down                                              | Args             | ✓ Locals      | ✓ Caller             | Task:               |                         |          |           |            | 65' Watch 65' View                         | ×      |

|              | ieve()<br>i = 6                                |                                                   |                  |               |                      | ^                   |                         |          |           |            | ft = 0xFFF0C438, ri<br>0, 1, 0, 0, 1, 1, 0 |        |

|              | primz                                          | = -998600                                         |                  |               |                      |                     |                         | (_, _, _ | , _, _, _ | , ,, _, _, | , 1, 0, 0, 1, 1, 1, 0                      | , ,, 1 |

|              | k = -9                                         |                                                   |                  |               |                      |                     |                         |          |           |            |                                            |        |

|              | anzahl                                         | = 0                                               |                  |               |                      |                     |                         |          |           |            |                                            |        |

| :            | anzah1                                         | = 0                                               |                  |               |                      |                     |                         |          |           |            |                                            |        |

| 001  m       | anzahl<br>ain()<br>j = 12                      | 345678                                            |                  |               |                      |                     |                         |          |           |            |                                            |        |

| 001  m       | anzahl<br>ain()<br>j = 12                      | -                                                 |                  |               |                      |                     |                         |          |           |            |                                            |        |

| 001  m       | anzahl<br>ain()<br>j = 12<br>p = 0x            | 345678                                            | RUE )            |               |                      |                     |                         |          |           |            |                                            |        |

| 001  mi<br>œ | anzahl<br>ain()<br>j = 12<br>p = 0x            | 345678<br>FFF0C324<br>while ( T<br>{              | RUE )<br>ieve(); |               |                      |                     |                         |          |           |            |                                            |        |

| 001  mi      | anzahl<br>ain()<br>j = 12<br>p = 0x            | 345678<br>FFF0C324<br>while ( T<br>{              |                  |               |                      | ~                   |                         |          |           |            |                                            |        |

| 001  m       | anzahl<br>ain()<br>j = 12<br>p = 0x            | 345678<br>FFF0C324<br>while ( T<br>{              |                  |               |                      | <b>↓</b>            | <                       |          |           |            |                                            | >      |

| 001  mi      | anzahl<br>ain()<br>j = 12<br>p = 0x<br>_init_m | 345678<br>FFF0C324<br>while ( T<br>{              |                  |               |                      |                     | <                       |          |           |            |                                            | > .    |

| 001  mi      | anzahl<br>ain()<br>j = 12<br>p = 0x<br>_init_m | 345678<br>FFF0C324<br>while ( T<br>{              |                  |               |                      |                     | K                       |          |           |            |                                            |        |

| 001  m       | <pre>anzahl ain() j = 12 p = 0x _init_m</pre>  | 345678<br>FFF0C324<br>while ( 1<br>{<br>sain(asm) |                  | Var           | List                 |                     | SYStem                  | Step     | Go        | Break      | other previo                               | 5(     |

All general commands are described in the "PowerView Command Reference" (ide\_ref.pdf) and "General Commands Reference".

[build 68859 - DVD 02/2016]

The extensive use of the TRACE32 Instruction Set Simulator requires a TRACE32 Simulator License.

For more information, see www.lauterbach.com/sim\_license.html.

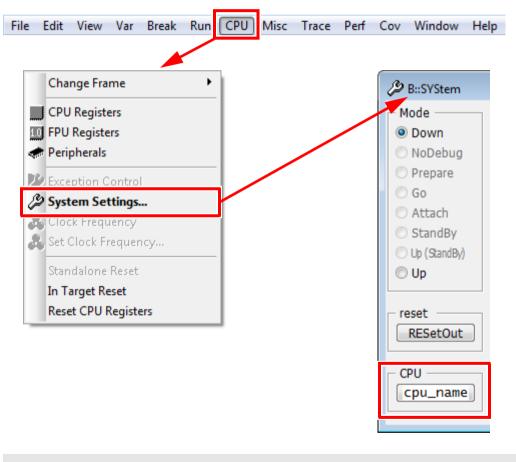

### To start the simulator, proceed as follows:

1. Select the device prompt for the Simulator and reset the system.

| B::   |  |  |  |

|-------|--|--|--|

| RESet |  |  |  |

The device prompt B:: is normally already selected in the TRACE32 command line. If this is not the case, enter B:: to set the correct device prompt. The **RESet** command is only necessary if you do not start directly after booting TRACE32.

2. Specify the CPU specific settings.

SYStem.CPU <cpu\_name>

The default values of all other options are set in such a way that it should be possible to work without modification. Please consider that this is probably not the best configuration for your target.

### 3. Enter debug mode.

SYStem.Up

This command resets the CPU and enters debug mode. After this command is executed it is possible to access memory and registers.

4. Load the program.

Data.LOAD.<file\_format> <file> ; load program and symbols

See the **Data.LOAD** command reference for a list of supported file formats. If uncertain about the required format, try **Data.LOAD.auto**.

A detailed description of the **Data.LOAD** command and all available options is given in the reference guide.

5. Start-up example

A typical start sequence is shown below. This sequence can be written to a PRACTICE script file (\*.cmm, ASCII format) and executed with the command DO *<file>*.

| B::                                                            | ; Select the ICD device prompt                        |

|----------------------------------------------------------------|-------------------------------------------------------|

| WinCLEAR                                                       | ; Clear all windows                                   |

| SYStem.CPU <cpu_name></cpu_name>                               | ; Select CPU type                                     |

| SYStem.Up                                                      | ; Reset the target and enter<br>; debug mode          |

| <pre>Data.LOAD.<file_format> <file></file></file_format></pre> | ; Load the application                                |

| Register.Set pc main                                           | ; Set the PC to function main                         |

| PER.view                                                       | ; Show clearly arranged<br>; peripherals in window *) |

| List.Mix                                                       | ; Open source code window *)                          |

| Register.view /SpotLight                                       | ; Open register window *)                             |

| Frame.view /Locals /Caller                                     | ; Open the stack frame with<br>; local variables *)   |

| Var.Watch %Spotlight flags ast                                 | ; Open watch window for<br>; variables *)             |

\*) These commands open windows on the screen. The window position can be specified with the **WinPOS** command.

For more information, see "API for TRACE32 Instruction Set Simulator" (simulator\_api.pdf).

# Troubleshooting

No information available

# FAQ

Please refer to https://support.lauterbach.com/kb.

The following memory classes are available:

| Memory Class | Description                       |

|--------------|-----------------------------------|

| Р            | Program                           |

| D            | Data                              |

| SPR          | Special Purpose Register          |

| DCR          | Device Control Register           |

| PMR          | Performance Control Register      |

| IC           | Instruction Cache                 |

| DC           | Data Cache                        |

| NC           | No Cache (only physically memory) |

If the cache is disabled, memory accesses to the memory classes IC or DC are realized by TRACE32-ICD as reads and writes to physical memory.

The instruction set simulator has built-in support for all core registers. The level of support varies by register. The first table lists all registers and their basic supported features, while the second table lists all registers that have support beyond the basic features.

| Register(s)                                                                                                                    | Basic supported features                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPR[031]<br>FPR[031] (*)<br>FPSCR<br>VR[031] (*)<br>VRSAVE (*)<br>VSCR (*)<br>CR<br>CTR<br>LR<br>XER<br>SPEFSCR (*)<br>ACC (*) | <b>Full support, e.g.:</b><br>View/modify through debugger views and commands<br>Source/destination register of opcodes (including status flags) of<br>standard PowerPC, SPE, EFPU, Altivec and VLE.<br>etc. |

| SPR<br>DCR<br>PMR                                                                                                              | If not stated otherwise in table with additional features:<br>View/modify through by debugger<br>Read/write by instruction (MFSPR/MTSPR etc.)                                                                |

Registers with additional features:

| Register(s)          | Additional features                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSR                  | Read/write/modify by instructions modifying MSR (MTMSR, MFMSR,<br>WRTEE, RFI, RFCI, RFMCI, RFDI, MPC5xx: EIE/EID)<br>Modified by exceptions<br>MSR[FP] evaluated for FPU<br>QorlQ; MSR[PR], MSR[GS] evaluated for guest register access<br>PPC4XX, MPX5XXX, QorlQ: MSR[EE] evaluated for fixed interval<br>timer, decrementer (TCR/TSR)<br>MPC74XX, MPC86XX, QorlQ: MSR[VEC] evaluated for Altivec<br>e300 cores: MSR[IP] interrupt prefix |

| SRR0/1               | Modified by exceptions                                                                                                                                                                                                                                                                                                                                                                                                                     |

| HID0 (*)             | HID0[TBEN]                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PVR                  | Reports processor version, value may differ from actual processor                                                                                                                                                                                                                                                                                                                                                                          |

| TBL/TBU (*)          | Incrementing with each executed instruction                                                                                                                                                                                                                                                                                                                                                                                                |

| DEC (*)<br>DECAR (*) | Decrementing, interrupt when passes through zero an MSR[EE] set.<br>Reloaded with DECAR value (if supported by core)                                                                                                                                                                                                                                                                                                                       |

| TCR/TSR (*)          | Support for decrementer, fixed interval timer and watchdog                                                                                                                                                                                                                                                                                                                                                                                 |

| MAS[06] (*)          | MPC5XXX: MMU simulation limited to support mixed FLE/VLE appli-<br>cations                                                                                                                                                                                                                                                                                                                                                                 |

| ESR (*)                                    | ESR[PTR] and ESR[VLE]                                   |

|--------------------------------------------|---------------------------------------------------------|

| IVPR/EVPR (*)<br>IVOR0/1/4/6/8/10 (*)      | Base address for interrupts handlers                    |

| L1CSR0, L1CSR1 (*)<br>L1FINV0, L1FINV1 (*) | MPC5XXX: evaluated for cache simulation (see SIM.CACHE) |

(\*): not available for all PowerPC cores.

# SYStem.CPU

Select CPU type

Format: SYStem.CPU <cpu>

*<cpu>*: **505** | **509** | **555** | **821** | **860** | ...

# SYStem.MemAccess

# Select run-time memory access method

| Format: | SYStem.MemAccess Enable   StopAndGo   Denied |

|---------|----------------------------------------------|

|         | SYStem.ACCESS (deprecated)                   |

| Enable<br>CPU (deprecated) | Memory access during program execution to target is enabled.                                                                                                                                                  |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Denied                     | Memory access during program execution to target is disabled.                                                                                                                                                 |

| StopAndGo                  | Temporarily halts the core(s) to perform the memory access. Each stop takes some time depending on the speed of the JTAG port, the number of the assigned cores, and the operations that should be performed. |

| SYStem.Mode Est | ablish the communication with the simulator |

|-----------------|---------------------------------------------|

|-----------------|---------------------------------------------|

| Format:        | SYStem.Mode <mode></mode>                                                        |

|----------------|----------------------------------------------------------------------------------|

|                | SYStem.Down (alias for SYStem.Mode Down)<br>SYStem.Up (alias for SYStem.Mode Up) |

| <mode>:</mode> | Down<br>NoDebug<br>Go<br>Up                                                      |

Default: Down.

Selects the target operating mode.

| Down    | The CPU is in reset. Debug mode is not active. Default state and state after fatal errors.                                                                     |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NoDebug | The CPU is running. Debug mode is not active. Debug port is tristate. In this mode the target should behave as if the debugger is not connected.               |  |

| Go      | The CPU is running. Debug mode is active. After this command the CPU can be stopped with the break command or if any break condition occurs.                   |  |

| Up      | The CPU is not in reset but halted. Debug mode is active. In this mode the CPU can be started and stopped. This is the most typical way to activate debugging. |  |

If the mode **Go** is selected, this mode will be entered, but the control button in the **SYStem.state** window jumps to the mode **Up**.

# SYStem.Option.Address32

# Define address format display

| Format: | SYStem.Option.Address32 [ON   OFF   AUTO   NARROW] |

|---------|----------------------------------------------------|

|---------|----------------------------------------------------|

### Default: AUTO.

Selects the number of displayed address digits in various windows, e.g. List.auto or Data.dump.

| ON                                                   | Display all addresses as 32-bit values. 64-bit addresses are truncated. |  |

|------------------------------------------------------|-------------------------------------------------------------------------|--|

| OFF                                                  | Display all addresses as 64-bit values.                                 |  |

| AUTO                                                 | Number of displayed digits depends on address size.                     |  |

| NARROW 32-bit display with extendible address field. |                                                                         |  |

| Format:        | SYStem.Option.DisMode <mode></mode> |

|----------------|-------------------------------------|

| <mode>:</mode> | ACCESS<br>AUTO<br>FLE<br>VLE        |

### MPC5XXX/SPC5XX only.

This command sets the operation mode for the simulator.

| AUTO (default) | Behavior depending on CPU selection. VLE/FLE operation for VLE/FLE-only processors, others: see ACCESS                         |

|----------------|--------------------------------------------------------------------------------------------------------------------------------|

| ACCESS         | Default: Standard PowerPC (FLE) instruction set. Simulator supports mixed FLE/VLE code execution if MMU simulation is enabled. |

| FLE            | Simulator is configured to execute code compiled for the standard PowerPC instruction set (fixed length encoding).             |

| VLE            | Simulator is configured to execute code compiled for VLE (variable length encoding).                                           |

# SYStem.Option.DUALPORT

# Run-time memory access for all windows

Format: SYStem.Option.DUALPORT [ON | OFF]

Default: OFF.

Dualport access of memory while simulation in running.

Format:

SYStem.Option.IMASKASM [ON | OFF]

Default: OFF.

If enabled, the interrupt mask bits of the CPU will be set during assembler single-step operations. The interrupt routine is not executed during single-step operations. After single step the interrupt mask bits are restored to the value before the step.

# **SYStem.Option.IMASKHLL** Disable interrupts while HLL single stepping

Format: SYStem.Option.IMASKHLL [ON | OFF]

Default: OFF.

If enabled, the interrupt mask bits of the cpu will be set during HLL single-step operations. The interrupt routine is not executed during single-step operations. After single step the interrupt mask bits are restored to the value before the step.

**NOTE:** Do not enable this option for code that disables MSR\_EE. The debugger will disable MSR\_EE while the CPU is running and restore it after the CPU stopped. If a part of the application is executed that disables MSE\_EE, the debugger cannot detect this change and will restore MSE\_EE.

| Format: |

|---------|

|---------|

SYStem.Option.MMUSPACES [ON | OFF] SYStem.Option.MMUspaces [ON | OFF] (deprecated) SYStem.Option.MMU [ON | OFF] (deprecated)

Default: OFF.

Enables the use of space IDs for logical addresses to support **multiple** address spaces.

For an explanation of the TRACE32 concept of address spaces (zone spaces, MMU spaces, and machine spaces), see "TRACE32 Concepts" (trace32\_concepts.pdf).

| NOTE: | SYStem.Option.MMUSPACES should not be set to ON if only one translation table is used on the target. |  |

|-------|------------------------------------------------------------------------------------------------------|--|

|       | If a debug session requires space IDs, you must observe the following sequence of steps:             |  |

|       | 1. Activate SYStem.Option.MMUSPACES.                                                                 |  |

|       | 2. Load the symbols with Data.LOAD.                                                                  |  |

|       | Otherwise, the internal symbol database of TRACE32 may become inconsistent.                          |  |

### Examples:

```

;Dump logical address 0xC00208A belonging to memory space with

;space ID 0x012A:

Data.dump D:0x012A:0xC00208A

;Dump logical address 0xC00208A belonging to memory space with

;space ID 0x0203:

Data.dump D:0x0203:0xC00208A

```

### Format: SYStem.Option.MACHINESPACES [ON | OFF]

### Default: OFF

Enables the TRACE32 support for debugging virtualized systems. Virtualized systems are systems running under the control of a hypervisor.

After loading a Hypervisor Awareness, TRACE32 is able to access the context of each guest machine. Both currently active and currently inactive guest machines can be debugged.

### If SYStem.Option.MACHINESPACES is set to ON:

Addresses are extended with an identifier called machine ID. The machine ID clearly specifies to which host or guest machine the address belongs.

The host machine always uses machine ID 0. Guests have a machine ID larger than 0. TRACE32 currently supports machine IDs up to 30.

- The debugger address translation (MMU and TRANSlation command groups) can be individually configured for each virtual machine.

- Individual symbol sets can be loaded for each virtual machine.

# **SYStem.Option.NOTRAP** Use alternative software breakpoint instruction

| Format:        | SYStem.Option.NOTRAP <type></type> |

|----------------|------------------------------------|

| <type>:</type> | ON   OFF   FPU   ILL               |

Defines which instruction is used to implement software breakpoints.

| OFF       | Use TRAP instructions as software breakpoint (default setting).                                    |  |

|-----------|----------------------------------------------------------------------------------------------------|--|

| ON<br>ILL | Using illegal opcode as breakpoint instruction, TRAP instruction available for use in application. |  |

| FPU       | Not supported in simulator. Same effect as ON.                                                     |  |

| Format:       | SYStem.Option.OVERLAY [ON   OFF   WithOVS]                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Default: OFF. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| ON            | Activates the overlay extension and extends the address scheme of the debugger with a 16 bit virtual overlay ID. Addresses therefore have the format <i><overlay_id>:<address></address></overlay_id></i> . This enables the debugger to handle overlaid program memory.                                                                                                                                                                                                                                      |  |

| OFF           | Disables support for code overlays.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| WithOVS       | Like option <b>ON</b> , but also enables support for software breakpoints. This means that TRACE32 writes software breakpoint opcodes to both, the <i>execution area</i> (for active overlays) and the <i>storage area</i> . This way, it is possible to set breakpoints into inactive overlays. Upon activation of the overlay, the target's runtime mechanisms copies the breakpoint opcodes to the execution area. For using this option, the storage area must be readable and writable for the debugger. |  |

### Example:

SYStem.Option.OVERLAY ON List.auto 0x2:0x11c4

; List.auto <overlay\_id>:<address>

# SYStem.Option.REALTIME Stall the simulator if faster than real processor

Format:

SYStem.Option.REALTIME [ON | OFF]

Default: OFF.

Prevents the simulator from runnig faster than the frequency set with VCO.Frequency (default: 10MHz).

### SYStem.Option.TranslationSPACE [ON | OFF]

Default: ON.

Format:

This system option configures the debugger how to distinguish between user and supervisor modes.

In bare-metal applications or uncomplex operating systems typically the MSR[IS] bit is used to isolate user from supervisor address space. There is no way to get the information about this bit within the trace information, the program trace will be decoded using the current context of the cores.

In complex or hypervisor systems, typically the MSR[PR] bit is used to handle user and supervisor modes. This bit will also be included in ownership trace messages. TRACE32 will therefore be able to decode the program trace depending on this privilege information, which doesn't have to be compliant to the current context of cores.

### a) SYStem.Option.TranslationSPACE ON (default)

| Mode                       | MSR.GS bit | MSR. <mark>IS</mark> bit |

|----------------------------|------------|--------------------------|

| Hypervisor-supervisor mode | 0          | 0                        |

| Hypervisor-user            | 0          | 1                        |

| Guest-supervisor           | 1          | 0                        |

| Guest-user                 | 1          | 1                        |

#### b) SYStem.Option.TranslationSPACE OFF

| Mode                       | MSR.GS bit | MSR. <mark>PR</mark> bit |

|----------------------------|------------|--------------------------|

| Hypervisor-supervisor mode | 0          | 0                        |

| Hypervisor-user            | 0          | 1                        |

| Guest-supervisor           | 1          | 0                        |

| Guest-user                 | 1          | 1                        |

[Example]

### Format: SYStem.Option.ZoneSPACES [ON | OFF]

Default: OFF.

The **SYStem.Option.ZoneSPACES** command must be set to **ON** if separate symbol sets and MMU translation tables are used for the CPU operation modes:

- Hypervisor-supervisor mode

- Hypervisor-user mode

- Guest-supervisor mode

- Guest-user mode

Within TRACE32, these CPU operation modes are referred to as zones. For information about the status bits controlling these modes, see **SYStem.Option.TranslationSPACE**.

| NOTE: | For an explanation of the TRACE32 concept of address spaces (zone spaces,                   |

|-------|---------------------------------------------------------------------------------------------|

|       | MMU spaces, and machine spaces), see " <b>TRACE32 Concepts</b> "<br>(trace32_concepts.pdf). |

In each CPU operation mode (zone), the CPU's TLB may contain separate translations, and a kernel or hypervisor may uses separate MMU translation tables for memory accesses and separate register sets. Consequently, in each zone, different code and data can be visible on the same logical address.

| OFF | TRACE32 does not separate symbols by access class. Loading two or<br>more symbol sets with overlapping address ranges will result in<br>unpredictable behavior. Loaded symbols are independent of the CPU<br>mode. |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ON  | Separate symbol sets can be loaded for each zone, even with overlapping address ranges. Loaded symbols are specific to one of the CPU zones.                                                                       |

### SYStem.Option.ZoneSPACES ON in Detail

SYStem.Option.ZoneSPACES is usually set to ON if you need to debug virtualized systems with guest and hypervisor. For both guest and hypervisor, TRACE32 also separates between supervisor mode and user mode. Typical scenarios use separate symbol sets for the hypervisor-supervisor mode, the guest-supervisor and the guest-user mode. The hypervisor-user mode is rarely used. The symbol sets are loaded to the access classes HS: (hypervisor-supervisor mode, GS: (guest-supervisor mode) and GU: (guest-user mode).

If **SYStem.Option.ZoneSPACES** is **ON**, TRACE32 enforces any memory address specified in a TRACE32 command to have an access class which clearly indicates to which of the four zones the memory address belongs.

If an address specified in a command uses an anonymous access class such as D:, P: or C:, the access class of the current PC context is used to complete the access class of the addresses. Also, if an incomplete access class where either the guest/hypervisor information is missing (such as SP: or UP:) or the supervisor/user information is missing (such as GP: or HP:), the missing information will automatically be expanded from the access class of the current PC context.

**Example**: If the CPU is currently in user mode, a memory access with the access class GP: will be expanded by TRACE32 to become GUP:

If a symbol is referenced by name, the associated access class of its zone will be used automatically, so that the memory access is done within the correct CPU mode context. As a result, the symbol's effective address will be translated to the physical address with the correct MMU translation table.

### Example 1

In this script, SYStem.Option.ZoneSPACES is used for a simple host and guest debugging.

```

SYStem.Option.ZoneSPACES ON

; 1. Load the Xen hypervisor symbols to the hypervisor-supervisor

; access class HS:

Data.LOAD.ELF xen-syms HS:0x0 /NoCODE

; 2. Load the vmlinux kernel symbols to the guest-supervisor access class

; GS:

Data.LOAD.ELF vmlinux GS:0x0 /NoCODE

; 3. Load the guest application symbols (the 'sieve' application in this

; example) to the guest-user access class GU:

Data.LOAD.ELF sieve GU:0x0 /NoCODE

```

Effect on the TRANSlation command group: SYStem.Option.ZoneSPACES ON enforces separate address spaces for the four zones HS:, HU:, GS: and GU:. Commands affecting the address translation, such as TRANSlation.Create, TRANSlation.COMMON, TRANSlation.Protect or MMU.FORMAT, must be executed individually for each of the four zones.

It is, however, possible to use the generic access classes G: and H: as "joker". This simplifies the scripts if identical translations for GS: and GU: are needed or identical translations for HS: and HU: are needed.

SYStem.Option.ZoneSPACES ON ; show the list of static translations created by the commands ; TRANSlation.Create and TRANSlation.COMMON TRANSlation.List ;1. the command TRANSlation.Create G:0x8000000--0x8FFFFFFF 0x0 ; is equivalent to the commands TRANSlation.Create GS:0x8000000--0x8FFFFFFF 0x0 TRANSlation.Create GU:0x80000000--0x8FFFFFFF 0x0 :2. the command TRANSlation.Create H:0xA000000--0xAFFFFFFF 0x0 ; is equivalent to the commands TRANSlation.Create HS:0xA0000000--0xAFFFFFFF 0x0 TRANSlation.Create HU:0xA0000000--0xAFFFFFFF 0x0 :3. the command TRANSlation.COMMON G:0xC0000000--0xFFFFFFF ; is equivalent to the commands TRANSlation.COMMON GS:0xC0000000--0xFFFFFFF TRANSlation.COMMON GU:0xC0000000--0xFFFFFFF

### MMU.DUMP

# Page wise display of MMU translation table

| Format:            | MMU.DUMP  [ <range>   <address>   <range> <root>  <br/><address> <root>] [/<option>]<br/>MMUdump (deprecated)</option></root></address></root></range></address></range>                            |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| :                  | PageTable<br>KernelPageTable<br>TaskPageTable <task_magic>   <task_id>   <task_name>   <space_id>:0x0<br/><cpu_specific_tables></cpu_specific_tables></space_id></task_name></task_id></task_magic> |

| <option>:</option> | <b>MACHINE</b> <machine_magic>   <machine_id>   <machine_name></machine_name></machine_id></machine_magic>                                                                                          |

Displays the contents of the CPU specific MMU translation table.

- If called without parameters, the complete table will be displayed.

- If the command is called with either an address range or an explicit address, table entries will only be displayed if their **logical** address matches with the given parameter.

| <root></root>                           | The <i><root></root></i> argument can be used to specify a page table base address deviating from the default page table base address. This allows to display a page table located anywhere in memory.                                                                                                                                                                     |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <range><br/><address></address></range> | Limit the address range displayed to either an address range<br>or to addresses larger or equal to <i><address></address></i> .<br>For most table types, the arguments <i><range></range></i> or <i><address></address></i> can also be<br>used to select the translation table of a specific process or a specific<br>machine if a space ID and/or a machine ID is given. |

| PageTable                               | <ul> <li>Displays the entries of an MMU translation table.</li> <li>if <i><range></range></i> or <i><address></address></i> have a space ID and/or machine ID: displays the translation table of the specified process and/or machine</li> <li>else, this command displays the table the CPU currently uses for MMU translation.</li> </ul>                                |

| KernelPageTable                         | Displays the MMU translation table of the kernel.<br>If specified with the MMU.FORMAT command, this command reads the<br>MMU translation table of the kernel and displays its table entries.                                                                                                                                                                               |

| <b>TaskPageTable</b><br><task_magic>  <br/><task_id>  <br/><task_name>  <br/><space_id>:<b>0x0</b></space_id></task_name></task_id></task_magic> | <ul> <li>Displays the MMU translation table entries of the given process. Specify one of the TaskPageTable arguments to choose the process you want. In MMU-based operating systems, each process uses its own MMU translation table. This command reads the table of the specified process, and displays its table entries.</li> <li>For information about the first three parameters, see "What to know about the Task Parameters" (general_ref_t.pdf).</li> <li>See also the appropriate OS Awareness Manuals.</li> </ul> |

|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MACHINE<br><machine_magic>  <br/><machine_id>  <br/><machine_name></machine_name></machine_id></machine_magic>                                   | This option is only available if <b>SYStem.Option.MACHINESPACES</b> is set to <b>ON</b> .<br>Dumps a page table of a virtual machine. The <b>MACHINE</b> option applies to <b>PageTable</b> and <b>KernelPageTable</b> and some <i><cpu_specific_tables></cpu_specific_tables></i> .<br>The parameters <i><machine_magic></machine_magic></i> , <i><machine_id></machine_id></i> and <i><machine_name></machine_name></i> are displayed in the <b>TASK.List.MACHINES</b> window.                                             |

## CPU specific Tables in MMU.DUMP

If both **SYStem.Option.ZoneSPACES** and **SYStem.Option.MACHINESPACES** are set to **ON**, then these CPU specific tables are available:

| SupervisorPT | Displays the supervisor mode page table of the machine specified with option <b>MACHINE</b> . |

|--------------|-----------------------------------------------------------------------------------------------|

| UserPT       | Displays the user mode page table of the machine specified with the option <b>MACHINE</b> .   |

If only SYStem.Option.ZoneSPACES is set to ON, then these CPU specific tables are available:

| HSPageTable | Displays the page table which is defined for the hypervisor supervisor mode. |

|-------------|------------------------------------------------------------------------------|

| HUPageTable | Displays the page table which is defined for the hypervisor user mode.       |

| GSPageTable | Displays the page table which is defined for the guest supervisor mode.      |

| GUPageTable | Displays the page table which is defined for the guest user mode.            |

[Examples]

| Format:            | MMU.FORMAT <format> [<base_address> [<logical_kernel_address_range><br/><physical_kernel_address>]] [/<option>]</option></physical_kernel_address></logical_kernel_address_range></base_address></format> |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <option>:</option> | MACHINE <machine_magic>   <machine_id>   <machine_name><br/>Hypervisormode   Guestmode   Supervisormode   Usermode</machine_name></machine_id></machine_magic>                                            |

The TRACE32 debugger address translation tries to perform page table walks when logical addresses are accessed through the debugger - either when an address is read from memory or for page table dumps or page table scans. If supported by the CPU architecture, the type and format of the page tables is extracted automatically from the hardware MMU registers. Command MMU.FORMAT can be used to manually specify the page table format, the page table base address and - optionally - an initial default translation which is used by TRACE32 to translate logical addresses used in the page table or the kernel itself to physical addresses.

For some architectures, multiple CPU modi with individual page tables exist (CPU zones). If a hypervisor is running, each virtual machine and the host machine also use individual page tables.

Using options **ACCESS**, **MACHINE** and **Intermediate** the parameters for each of these page tables can be specified individually.

### <format>

<format> is to be replaced with a CPU architecture specific keyword which defines the structure of the MMU page tables used by the kernel. By default, TRACE32 assumes that the MMU format is **STD**, unless *you* specify the **MMU.FORMAT** <*format*> explicitly.

| <format></format> | Description                                                                                                                           |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| DEOS              | DEOS OS (32 bit) specific MMU format                                                                                                  |

| DEOS64            | DEOS OS (64 bit) specific MMU format                                                                                                  |

| EXTENSION         | Table walk performed by a TRACE32 extension that<br>a) was developed by the customer and<br>b) defines table walk callback functions. |

| LINUX             | Standard format used by Linux                                                                                                         |

| LINUX26           | Linux format with physical table pointers                                                                                             |

| LINUX64_E6        | Use LINUX64_E6 for e6500 core devices                                                                                                 |

| LINUXE5           | Linux with 64-bit PTEs, e500 core                                                                                                     |

| LINUXEXT          | Linux with 64-bit PTEs, no e500 core                                                                                                  |

| <format></format> | Description                                                                                                                                                                |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LYNXOS            | LynxOS format, virtual table pointers                                                                                                                                      |

| LYNXOSPHYS        | LynxOS format, physical table pointers                                                                                                                                     |

| OSE               | OSE format for load modules                                                                                                                                                |

| PIKEOS.E500       | PIKEOS specific format for PowerPC e500 core (formerly named<br>PIKEOSE5).Works for PikeOS 4.1 and older. For e500 cores with PikeOS<br>4.2 and newer use E500MC format.*/ |

| PIKEOS.E500MC     | PIKEOS specific format for PowerPC e500mc core (PPC64 only).Can also be used with PikeOS 4.2 and newer on PPC32 e500 cores.*/                                              |

| PIKEOS.E500MC4G   | PIKEOS specific format for PowerPC e500mc core addressing 4GB of memory.Has no common address range.*/                                                                     |

| PIKEOS.E5500      | PIKEOS specific format for PowerPC e5500 core                                                                                                                              |

| PIKEOS.OEA        | PIKEOS specific format for PowerPC core (formerly named PIKEOS) */                                                                                                         |

| QNX               | QNX standard format                                                                                                                                                        |

| QNXBIG            | QNX format with 64-bit table entries                                                                                                                                       |

| STD               | Standard format defined by the CPU                                                                                                                                         |

| VX653             | MMU format for VXWORKS 653                                                                                                                                                 |

| VXWORKS.E500      | VxWorks specific format for PowerPC e500 core                                                                                                                              |

| VXWORKS.E500MC    | VxWorks specific format for PowerPC e500mc core with 36 bit physical addresses (PPC64 only)                                                                                |

| VXWORKS.E500_64   | VxWorks specific format for PowerPC e500 core (PPC64 only)                                                                                                                 |

| VXWORKS.E6500     | VxWorks specific format for PowerPC e6500 core                                                                                                                             |

### <base\_address>

*<base\_address>* defines the start address of the default page table which is usually the kernel page table. The kernel page table contains translations for mapped address ranges owned by the kernel.

The debugger address translation uses the default page table if no process specific page table (task page table) is available to translate an address.

*<base\_address>* can be left empty by typing a comma or set to zero if there is no default page table available in the system.

### logical\_kernel\_address\_range> and <physical\_kernel\_address> for the Default Translation

The arguments <*logical\_kernel\_address\_range*> and <*physical\_kernel\_address>* define a linear logical-tophysical address translation for the kernel addresses, called *kernel translation* or *default translation*. This translation should cover all statically mapped logical address ranges of kernel code or kernel data.

For the <physical\_kernel\_address> you just need to specify the start address.

# **NOTE:** If no kernel translation is specified for a given memory access, TRACE32 tries to use static address translations defined by the command **TRANSlation.Create**. The kernel translation is shown in the **TRANSlation.List** window.

| Supervisormode | If <b>SYStem.Option.MACHINESPACES</b> is set to <b>OFF</b> :<br>Specifies the format, default page table, and default translation for one or<br>both supervisor zones (access class HS: or GS:). Can be combined with<br>the <b>Hypervisormode</b> or <b>Guestmode</b> option.<br>If <b>SYStem.Option.MACHINESPACES</b> is set to <b>ON</b> :<br>Specifies the format, default page table, and default translation for the<br>supervisor mode zone of the machine selected with the <b>MACHINE</b><br>option.<br>For an example, see below. |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Usermode       | If <b>SYStem.Option.MACHINESPACES</b> is set to <b>OFF</b> :<br>Specifies the format, default page table, and default translation for one or<br>both user mode zones (access class HU: or GU:). Can be combined with<br>the <b>Hypervisormode</b> or <b>Guestmode</b> option.                                                                                                                                                                                                                                                               |

|                | If <b>SYStem.Option.MACHINESPACES</b> is set to <b>ON</b> :<br>Specifies the format, default page table, and default translation for the<br>user mode zone of the machine which is selected with the <b>MACHINE</b><br>option.                                                                                                                                                                                                                                                                                                              |

| Hypervisormode | Specifies the format, default page table, and default translation for one or both hypervisor zones (access class HS: or HU:). Can be combined with the <b>Supervisormode</b> or <b>Usermode</b> option.                                                                                                                                                                                                                                                                                                                                     |

|                | For an example, see below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Guestmode      | Specifies the format, default page table, and default translation for one or both guest zones (access class GS: or GU:). Can be combined with the <b>Supervisormode</b> or <b>Usermode</b> option.                                                                                                                                                                                                                                                                                                                                          |

| MACHINE        | For a description of the <b>MACHINE</b> option, see <b>MMU.DUMP</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

If both **SYStem.Option.ZoneSPACES** and **SYStem.Option.MACHINESPACES** are set to **ON**, then these options are available:

- MACHINE

- Supervisormode

- Usermode

If only SYStem.Option.ZoneSPACES is set to ON, then these options are available:

- Hypervisormode

- Guestmode

- Supervisormode

- Usermode

If only SYStem.Option.MACHINESPACES is set to ON, then these option is available:

• MACHINE

### Examples for Page Tables in Virtualized Systems

[Back to MMU.FORMAT]

| NOTE: | <ul> <li>The MMU format and default page table base address of each zone can be viewed with the command TRANSlation.state.</li> <li>The default translation of each zone can be viewed with the command TRANSlation.List</li> </ul> |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                                                                                     |

**Example 1**: This script shows how to define separate default page tables and separate default translations for various zones (*without* Hypervisor Awareness and *without* machine IDs). The backslash \ is used as a line continuation character. No white space permitted after the backslash.

; enable symbol management for zones SYStem.Option.ZoneSPACES ON ; define the format for the hypervisor-supervisor zone (access class HS:) MMU.FORMAT STD HS:0xC8000000 HS:0x8000000++0x0FFFFFF A:0x00000000 /Hypervisormode /Supervisormode ; define the format for the hypervisor-user zone (access class HU:) MMU.FORMAT STD HU:0x34000000 HU:0x3000000++0x0FFFFFF A:0x00800000 /Hypervisormode /Usermode ; define the format for guest-supervisor zone (access class GS:) MMU.FORMAT VX653 GS:0xA4000000 GS:0xA0000000++0x0FFFFFF A:0x10000000 /Guestmode /Supervisormode ; define the format for guest-user zone (access class GU:) MMU.FORMAT VX653 GU:0x22000000 GU:0x2000000++0x1FFFFFF A:0x18000000 /Guestmode /Usermode ; show the result of the format definition TRANSlation.state TRANSlation.List

**Example 2**: This script shows how to define separate default page tables and separate default translations for various zones (with Hypervisor Awareness and with machine IDs). The backslash \ is used as a line continuation character. No white space permitted after the backslash.

```

; enable symbol management for zones

SYStem.Option.ZoneSPACES ON

; enable address extension for guest OSes

SYStem.Option.MACHINESPACES ON

; define the format for the supervisor zone of machine 0

; (access class HS:)

MMU.FORMAT STD HS:0:::0xC8000000 HS:0:::0x80000000++0x0FFFFFF

A:0x0000000 /MACHINE 0 /Supervisormode

; define the format for the supervisor zone of machine 1

; (access class GS:)

MMU.FORMAT STD GS:1:::0xA4000000 GS:1:::0xA0000000++0x0FFFFFF

A:0x10000000 /MACHINE 1 /Supervisormode

; define the format for the guest-user zone of machine 1

; (access class GU:)

MMU.FORMAT VX653 GU:1:::0x22000000 GU:1:::0x20000000++0x1FFFFFF

١

A:0x18000000 /MACHINE 1 /Usermode

; define the format for both the guest-supervisor zone and the guest-user

; zone of machine 2 concurrently (access class G:)

MMU.FORMAT VX653 G:0xB8000000 G:0xB0000000++0x1FFFFFF

١

A:0x40000000 /MACHINE 2

; show the result of the format definition

TRANSlation.state

TRANSlation.List

```

| Format:            | MMU.List  [ <range>   <address>   <range> <root>   <address> <root>]<br/>[/<option>]<br/>MMUList (deprecated)</option></root></address></root></range></address></range>                            |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| :                  | PageTable<br>KernelPageTable<br>TaskPageTable <task_magic>   <task_id>   <task_name>   <space_id>:0x0<br/><cpu_specific_tables></cpu_specific_tables></space_id></task_name></task_id></task_magic> |

| <option>:</option> | <b>MACHINE</b> <machine_magic>   <machine_id>   <machine_name></machine_name></machine_id></machine_magic>                                                                                          |

Lists the address translation of the CPU-specific MMU table.

- If called without address or range parameters, the complete table will be displayed.

- If called without a table specifier, this command shows the debugger-internal translation table. See **TRANSlation.List**.

- If the command is called with either an address range or an explicit address, table entries will only be displayed if their **logical** address matches with the given parameter.

| <root></root>                           | The <i><root></root></i> argument can be used to specify a page table base address deviating from the default page table base address. This allows to display a page table located anywhere in memory.                                                                                                                                                                     |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <range><br/><address></address></range> | Limit the address range displayed to either an address range<br>or to addresses larger or equal to <i><address></address></i> .<br>For most table types, the arguments <i><range></range></i> or <i><address></address></i> can also be<br>used to select the translation table of a specific process or a specific<br>machine if a space ID and/or a machine ID is given. |

| PageTable                               | <ul> <li>Lists the entries of an MMU translation table.</li> <li>if <i><range></range></i> or <i><address></address></i> have a space ID and/or machine ID: list the translation table of the specified process and/or machine</li> <li>else, this command lists the table the CPU currently uses for MMU translation.</li> </ul>                                          |

| KernelPageTable                         | Lists the MMU translation table of the kernel.<br>If specified with the MMU.FORMAT command, this command reads the<br>MMU translation table of the kernel and lists its address translation.                                                                                                                                                                               |

| <b>TaskPageTable</b><br><task_magic>  <br/><task_id>  <br/><task_name>  <br/><space_id><b>:0x0</b></space_id></task_name></task_id></task_magic> | <ul> <li>Lists the MMU translation of the given process. Specify one of the TaskPageTable arguments to choose the process you want.</li> <li>In MMU-based operating systems, each process uses its own MMU translation table. This command reads the table of the specified process, and lists its address translation.</li> <li>For information about the first three parameters, see "What to know about the Task Parameters" (general_ref_t.pdf).</li> <li>See also the appropriate OS Awareness Manuals.</li> </ul> |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MACHINE                                                                                                                                          | For a description of the <b>MACHINE</b> option, see <b>MMU.DUMP</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

## CPU specific Tables in MMU.List

If both **SYStem.Option.ZoneSPACES** and **SYStem.Option.MACHINESPACES** are set to **ON**, then these CPU specific tables are available:

| SupervisorPT | Displays the supervisor mode page table of the machine specified with option <b>MACHINE</b> . |

|--------------|-----------------------------------------------------------------------------------------------|

| UserPT       | Displays the user mode page table of the machine specified with the option <b>MACHINE</b> .   |

If only SYStem.Option.ZoneSPACES is set to ON, then these CPU specific tables are available:

| HSPageTable | Displays the page table which is defined for the hypervisor supervisor mode. |

|-------------|------------------------------------------------------------------------------|

| HUPageTable | Displays the page table which is defined for the hypervisor user mode.       |

| GSPageTable | Displays the page table which is defined for the guest supervisor mode.      |

| GUPageTable | Displays the page table which is defined for the guest user mode.            |

| Format:            | MMU.SCAN  [ <range> <address>] [/<option>]<br/>MMUSCAN (deprecated)</option></address></range>                                                                                                              |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| :                  | PageTable<br>KernelPageTable<br>TaskPageTable <task_magic>   <task_id>   <task_name>   <space_id>:0x0<br/>ALL<br/><cpu_specific_tables></cpu_specific_tables></space_id></task_name></task_id></task_magic> |

| <option>:</option> | <b>MACHINE</b> <machine_magic>   <machine_id>   <machine_name></machine_name></machine_id></machine_magic>                                                                                                  |

Loads the CPU-specific MMU translation table from the CPU to the debugger-internal static translation table.

- If called without parameters, the complete page table will be loaded. The list of static address translations can be viewed with **TRANSlation.List**.

- If the command is called with either an address range or an explicit address, page table entries will only be loaded if their **logical** address matches with the given parameter.

Use this command to make the translation information available for the debugger even when the program execution is running and the debugger has no access to the page tables and TLBs. This is required for the real-time memory access. Use the command **TRANSlation.ON** to enable the debugger-internal MMU table.

| PageTable                                                                                                                                        | <ul> <li>Loads the entries of an MMU translation table and copies the address translation into the debugger-internal static translation table.</li> <li>if <i><range></range></i> or <i><address></address></i> have a space ID and/or machine ID: loads the translation table of the specified process and/or machine</li> <li>else, this command loads the table the CPU currently uses for MMU translation.</li> </ul>                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|