# Application Note for Complex Trigger Language

Release 02.2025

**MANUAL**

# Application Note for Complex Trigger Language

---

[TRACE32 Online Help](#)

[TRACE32 Directory](#)

[TRACE32 Index](#)

|                                                                     |                                                                                     |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| <a href="#">TRACE32 Documents</a> .....                             |  |

| <a href="#">Complex Trigger Language</a> .....                      |  |

| <a href="#">Application Note for Complex Trigger Language</a> ..... | 1                                                                                   |

| <a href="#">History</a> .....                                       | 5                                                                                   |

| <a href="#">Introduction</a> .....                                  | 6                                                                                   |

| <a href="#">Basic Structure of CTL Programs</a> .....               | 7                                                                                   |

| Complex Statements                                                  | 8                                                                                   |

| Agents                                                              | 9                                                                                   |

| Core Agents                                                         | 9                                                                                   |

| Bus Monitors                                                        | 11                                                                                  |

| Default Agent                                                       | 11                                                                                  |

| State Machines                                                      | 12                                                                                  |

| Using CTL State Machines                                            | 12                                                                                  |

| Multiple State Machines                                             | 13                                                                                  |

| <a href="#">TRACE32 Commands Using CTL Programs</a> .....           | 14                                                                                  |

| CTL Onchip Triggers Logic                                           | 14                                                                                  |

| CTL for Trace Find                                                  | 14                                                                                  |

| CTL Streaming Trace Trigger                                         | 15                                                                                  |

| <a href="#">CTL for Onchip Triggers Logic</a> .....                 | 16                                                                                  |

| CTL for TriCore MCDS                                                | 17                                                                                  |

| Supported Targets                                                   | 17                                                                                  |

| Multicore Support                                                   | 17                                                                                  |

| Selective Bus Trace                                                 | 17                                                                                  |

| Automatic Configuration of the Trace Source Multiplexers            | 18                                                                                  |

| TriCore Data Trace: COREx Vs. SRI-CPUx                              | 18                                                                                  |

| Limitations                                                         | 19                                                                                  |

| Examples                                                            | 20                                                                                  |

| CTL for Arm ETM                                                     | 31                                                                                  |

| Supported Targets                                                   | 31                                                                                  |

| Limitations                                                         | 31                                                                                  |

| Examples                                                            | 31                                                                                  |

| <a href="#">Examples for CTL Trace Find</a> .....                   | 36                                                                                  |

| Use case 1: Checking Variable Access                                | 36                                                                                  |

|                                                            |                                             |

|------------------------------------------------------------|---------------------------------------------|

| Use case 2: Checking Timing Constraints - Address Duration | 38                                          |

| Use case 3: Checking Timing Constraints - Address Distance | 40                                          |

| <b>Keyword Reference: CTL Conditions/Triggers .....</b>    | <b>42</b>                                   |

| BREAKPOINT                                                 | ABCDE breakpoint                            |

| BusTrigger                                                 | Incoming trigger signal                     |

| BMC                                                        | Benchmark counter event                     |

| COUNT                                                      | Trigger on event counter                    |

| CLOCKS                                                     | Trigger on clock cycles counter             |

| CTM                                                        | Cross trigger                               |

| EXTIN                                                      | External input                              |

| FALSE                                                      | Never condition                             |

| FLAG                                                       | Flag status                                 |

| MACHINE                                                    | Machine comparator                          |

| Program                                                    | Program access comparator                   |

| ProgramFail                                                | Conditional instruction execution           |

| ProgramPass                                                | Conditional instruction execution           |

| Read                                                       | Read access                                 |

| ReadWrite                                                  | Read or write access                        |

| SingleShot                                                 | Single shot comparators                     |

| SingleShot.Program                                         | Single shot program execution               |

| SingleShot.ProgramFail                                     | Single shot conditional execution           |

| SingleShot.ProgramPass                                     | Single shot conditional execution           |

| SingleShot.Read                                            | Single shot read access                     |

| SingleShot.ReadWrite                                       | Single shot read or write access            |

| SingleShot.Write                                           | Single shot write access                    |

| NoSingleShot                                               | Non single shot comparators                 |

| NoSingleShot.Program                                       | Non single shot program execution           |

| NoSingleShot.ProgramFail                                   | Non single shot conditional execution       |

| NoSingleShot.ProgramPass                                   | Non single shot conditional execution       |

| NoSingleShot.Read                                          | Non single shot read access                 |

| NoSingleShot.ReadWrite                                     | Non single shot read or write access        |

| NoSingleShot.Write                                         | Non single shot write access                |

| STATE.LEAVE                                                | Leave the state transition (edge sensitive) |

| STATE.ENTER                                                | Enter the state transition (edge sensitive) |

| STATE.TRACEON                                              | Active state of a TraceON action            |

| TASK                                                       | Task comparator                             |

| TIME                                                       | Time counter comparator                     |

| TRUE                                                       | Always condition                            |

| Var                                                        | Specify source-level expressions            |

| Var.Program                                                | Flat function execution                     |

| Var.Read                                                   | Variable read access                        |

| Var.ReadWrite                                              | Variable read or write access               |

| Var.status                                                 | tbd.                                        |

|                                       |                                                      |           |

|---------------------------------------|------------------------------------------------------|-----------|

| Var.Write                             | Variable write access                                | 58        |

| Write                                 | Write access                                         | 59        |

| ZONE                                  | Zone comparator                                      | 59        |

| <b>Keyword Reference: CTL Actions</b> |                                                      | <b>60</b> |

| Break                                 | Stop the program execution                           | 60        |

| BusCLOCKS                             | tbd.                                                 | 60        |

| BusCount                              | tbd.                                                 | 60        |

| BusTIME                               | tbd.                                                 | 60        |

| BusTrigger                            | tbd.                                                 | 61        |

| CLEAR                                 | Clear flag                                           | 61        |

| CTM                                   | Cross trigger                                        | 61        |

| ENABLE                                | Enable counter                                       | 62        |

| EVENT                                 | Trace event                                          | 62        |

| EXTOUT                                | External output                                      | 63        |

| FOUND                                 | Add the trace sample to the search items result      | 63        |

| GOTO                                  | Change active state                                  | 63        |

| INCrement                             | Increment counter                                    | 64        |

| RELOAD                                | Reload counter                                       | 64        |

| SET                                   | Set flag                                             | 65        |

| Spot                                  | Shortly stop the program execution                   | 65        |

| TraceData                             | Sample specified data event                          | 66        |

| TraceEnable                           | Enable the trace on the specified event              | 67        |

| TraceOFF                              | Switch OFF the trace sampling                        | 68        |

| TraceON                               | Switch ON the trace sampling                         | 69        |

| TraceTIME                             | tbd.                                                 | 69        |

| TraceTrigger                          | Stop sampling to the trace buffer on specified event | 69        |

| <b>CTL Programming Errors</b>         |                                                      | <b>70</b> |

## History

---

15-Aug-2024 Added subchapter '[CTL for Arm ETM](#)'.

15-Feb-2023 Added onchip CTL support for miniMCDS.

29-Jun-2022 Initial version.

**NOTE:**

**This manual is still under construction.**

Complex Trigger Language (CTL) is a high-level parallel programming language. The main idea behind CTL is to offer TRACE32 users a simple and powerful interface to debug and trace complex scenarios without any specific knowledge about the low-level onchip triggers logic. The language is defined to grant a fine control of the debug logic and trace sources. CTL enables the user to fully benefit from the debug and trace capabilities offered by the target while keeping the entire focus on debugging and testing.

Additionally to onchip triggers logic, CTL supports **Trace.Find** as a target. This empowers TRACE32 with an advanced trace find feature. When operating in SPY mode, the trace find results could be used as a test vehicle for onchip triggers. This enables CTL for targets that do not provide any hardware support to implement complex triggers.

This document is divided into the following sections:

1. **Basic Structure of CTL Programs**

2. **TRACE32 Commands Using CTL Programs**

3. **CTL for Onchip Triggers Logic**

Separate sub-sections discuss peculiarities of each implementation for onchip CTL and present selected use cases with example CTL programs:

- **CTL for TriCore MCDS**

- **CTL for Arm ETM**

4. **Examples for CTL Trace Find**

5. **Keyword Reference: CTL Conditions/Triggers**

6. **Keyword Reference: CTL Actions**

7. **CTL programming errors**

**NOTE:**

In this document, simple triggers refer to breakpoints that are enabled via **Break.Set** commands. CTL is not intended to replace simple triggers, although most breakpoints could be easily written in CTL as well. The reason is that the onchip trigger unit programmed by CTL might behave differently from the trigger logic programmed by simple triggers. E.g. for TriCore the stopping breakpoints set via simple triggers are programmed to OCDS (break-before-make breakpoints). While the CTL **Break** actions are programmed to MCDS (the cores are stopped a few instructions after the trigger event).

# Basic Structure of CTL Programs

---

CTL makes an abstraction of the target architecture whenever possible. Apart from a few exceptions, e.g. special bus agents, the syntax is architecture-independent and valid for all CTL targets.

Following is the list of elements composing CTL programs:

- Complex statements

- Agents (optional)

- Levels (optional)

- Comments (start with // or ; and end with the next line break).

```

; this is a comment

// this is also a comment

[<agent>::]

[<level>:]

IF <condition>    ; this is another comment

<action>

```

CTL is **not** white space sensitive, but it is recommended to use indentations for better readability of the program.

CTL keywords are **not** case-sensitive. The following examples of CTL programs are similar:

```

if var.program(sieve)

traceenable program

```

```

IF Var.Program(sieve)

TraceEnable Program

```

Upper case letters indicate the short forms of CTL keywords and must not be omitted. All lower case letters can be omitted. Following is a short form of the above example program:

```

if v.p(sieve)

te p

```

# Complex Statements

---

Complex statements are the basic elements of any CTL program.

Each complex statement is composed of:

- One condition

- One or multiple action(s) to be performed when the condition is satisfied

A CTL condition starts with the keyword `IF` followed by a logical combination of one or more sub-expressions. The condition's sub-expressions could be issued from different or similar qualifier types (program comparators, memory address comparators, access types,...).

A line break separates the condition from its associated action(s).

Multiple actions of a complex statement must be separated by line breaks.

## Example:

```

// Enable program trace for the first instruction of the function sieve

IF Program(ENTRY:sieve)

TraceEnable Program

```

Details about CTL conditions and actions are provided in the following sections:

- [Keyword Reference: CTL Conditions/Triggers](#)

- [Keyword Reference: CTL Actions](#)

### NOTE:

Given that CTL is a parallel programming language, the order in which the complex statements appear in a CTL program is not important. All the complex statements are evaluated in parallel.

If the CTL program is implementing a state machine, all the complex statements belonging to the active state are evaluated in parallel. Complex statements belonging to the inactive levels of the state machine are not evaluated.

# Agents

---

Each CTL condition is evaluated for a specified agent, and likewise, each CTL action is to be performed by a specified agent. The syntax to specify an agent is as follows:

```

<agent_name>::

```

The CTL syntax allows using agents with global scopes or local scopes.

Local scope agents are to be specified as prefixes to the associated actions and/or sub-expressions of the CTL conditions.

## Example:

```

IF CORE0::Program(ENTRY:sieve0) || CORE1::Program(ENTRY:sieve1)

INCrement mycounter

```

An agent that is not prefixing any action or condition's sub-expression is a global scope agent.

The scope of a global agent starts from the specification of the agent name and ends with the specification of another global scope agent name.

## Example:

```

CORE0:::

IF Program(sieve0)

TraceEnable Program

IF Var.Write(msstatic1)

TraceEnable Write Address Data

CORE1:::

IF Var.Program(func2)

TraceEnable Write Address Data

```

Two types of agents are to be distinguished:

- Core agents

- Bus agents/monitors

## Core Agents

---

The syntax to specify a core agent is as follows:

```

CORE<n>::

```

The index *n* refers to the logical core number controlled by the TRCAE32 PowerView instance.

`SplitCORE::` and `JoinCORE::` are multicore agents. These are used to specify that a complex statement is to be evaluated for all the cores that are assigned to the PowerView instance (except for limitations from the target). The difference between `SplitCORE::` and `JoinCORE::` is as follows:

- `SplitCORE::` specifies that each statement is to be evaluated for each core separately.

- `JoinCORE::` specifies that all cores collaborate to evaluate a statement.

### **Example 1:**

The TRACE32 PowerView instance is controlling 2 cores of the target CPU (**CORE.ASSIGN 1. 2.**).

In the following CTL program `CORE1::` is used as global scope agent:

```

CORE1::

IF Var.Write(mstatic)

TraceEnable Program

```

This enables program flow trace of the second core if write access to the variable `mstatic` is performed by the same core.

### **Example 2:**

The TRACE32 PowerView instance is controlling 2 cores of the target CPU (**CORE.ASSIGN 1. 2.**).

In the following CTL program `SplitCORE::` is used as a global scope agent:

```

SplitCORE::

IF Var.Write(mstatic)

TraceEnable Program

```

When loading this CTL program, the complex statements is programmed for both cores separately. This means that:

- The program flow trace of the first core is enabled when the latter performs a write access to the variable `mstatic`.

- The program flow trace of the second core is enabled when the latter performs a write access to the variable `mstatic`.

### **Example 3:**

The TRACE32 PowerView instance is controlling 2 cores of the target CPU (**CORE.ASSIGN 1. 2.**).

In the following CTL program `JoinCORE::` is used as global scope agent:

```

JoinCORE::

IF Var.Write(mstatic)

TraceEnable Program

```

When loading this CTL program, both cores collaborate to evaluate the complex statement. This means that the program flow trace of both cores is enabled when one of both cores performs a write access to the variable `mstatic`.

## Bus Monitors

---

When using bus agents the trace sources are observed at the level of bus transactions. Thus, no program trace or program triggers are available for bus agents.

The list of bus agents is architecture-dependent. The list of available agents varies also depending on the target CPU.

In some cases, the bus name is used as the CTL agent. In other cases, bus agents refer either to bus masters initiating the transaction (e.g. DMA) or bus slaves incurring the transaction (e.g. memory units).

### Examples of bus agents:

- `SPB::` is to be used for observing the transactions on the Shared Peripheral Bus (SPB) of a TriCore AURIX device.

- `SRI-LMU::` is to be used for observing accesses to Local Memory Unit and EMEM of an AURIX TC2x device via the Shared Resource Interface (SRI) fabric.

- `SRI-DMA::` is to be used for observing DMA transactions on AURIX TC3x device via the SRI fabric.

## Default Agent

---

If no agent is specified, `SplitCORE::` is used as the default agent.

In the following example, both CTL programs are equivalent.

### Example:

```

IF Var.Program(sieve)

TraceEnable Program

```

```

SplitCORE::

IF Var.Program(sieve)

TraceEnable Program

```

## Using CTL State Machines

---

State machines could be used for debugging sequential events. The syntax to specify levels of state machines is as follows:

```

<level_name>:

```

The scope of a state machine level starts from the specification of the level name and ends with the specification of another level name.

The complex statements belonging to the scope of a state machine level are only evaluated when the level is active.

The first level specified in a CTL program is handled as the start level.

Transitions between different levels of a state machine are to be specified using **GOTO** *<target\_level>* actions.

### Example:

```

CORE0:::

start:

// transition to level1 statement

IF Program(ENTRY:sieve)

GOTO level1

level1:

// transition back to start level

IF Program(RETURN:sieve)

GOTO start

// stopping statement

IF Var.Write(mstatic1==2)

Break

```

In this example, the CTL program implements a state machine with 2 levels/states.

The state machine is initially at the **start** state. As soon as **core0** executes the entry point of **sieve()** function, a state transition to **level1** occurs. When executing the return instruction of the function **sieve()**, a state transition back to the level **start** occurs.

This implicates that **level1** is active as long as **core0** is executing the function **sieve()** or one of its nested functions. The level **start** is active otherwise.

Only when **level1** is active the stopping statement is evaluated.

Activating this CTL program will cause the target to **Break** when the following conditions are fulfilled:

- The agent `core0` is executing the function `sieve()` or one of its nested functions.

- The agent `core0` writes the value 2 to the variable `mstatic1`.

If initially, `core0` is already in `sieve()`, the stopping statement would not be evaluated until the next execution of `sieve()`, triggering a state machine transition to `level1`.

## Multiple State Machines

---

CTL allows programming multiple state machines. Levels that belong to a state machine are to be prefixed by the state machine name as follows:

```

<state_machine>.<level_name>:

```

### Example:

In the following CTL program `m1` and `m2` are independent state machines:

- `m1` specifies that the target is to be stopped if `func1()` is called by `func9()` or one of its nested functions.

- `m2` specifies that the target is to be stopped if the variable `mstatic1` is written outside `func2()` or one of its nested functions.

```

-----

// implementation of the state machine m1

-----

m1.start:

IF Program(ENTRY:func9)

GOTO m1.level1

m1.level1:

IF Program(RETURN:func9)

GOTO m1.start

IF Program(ENTRY:func1)

Break

-----

// implementation of the state machine m2

-----

m2.level0:

IF Program(ENTRY:func2)

GOTO m2.level1

IF Var.Write(mstatic1)

Break

m2.level1:

IF Program(RETURN:func2)

GOTO m2.level0

```

# TRACE32 Commands Using CTL Programs

---

CTL could be used with different targets:

- CTL for Onchip Triggers Logic

- CTL for Trace Find

- CTL Streaming Trace Trigger

This section presents different CTL targets and their corresponding TRACE32 commands.

## CTL Onchip Triggers Logic

---

CTL for onchip trigger logic (or Onchip CTL) requires that the target CPU provides the onchip logic to implement complex triggers. While the complexity level is limited by the onchip resources provided by the trigger unit, onchip CTL has the fastest response time compared to other CTL targets.

The following table recapitulates the list of TRACE32 commands that are used for onchip CTL.

|                          |                                                                                                    |

|--------------------------|----------------------------------------------------------------------------------------------------|

| <b>Break.Program</b>     | Opens interactive softkey-driven editor for CTL programs                                           |

| <b>Break.ReProgram</b>   | Activates existing program file                                                                    |

| <b>Break.ViewProgram</b> | Opens a window that shows the state of the CTL trigger unit                                        |

| <b>Break.CLEAR</b>       | Resets onchip trigger logic that is programmed by CTL. This command doesn't reset simple triggers. |

More information about CTL onchip triggers can be found in the chapter [CTL for Onchip Triggers Logic](#).

## CTL for Trace Find

---

Using CTL for trace find allows searching for the occurrence(s) of complex events in the trace recording, e.g. sequential events happening in a specific or even arbitrary order.

After the CTL program for trace find is activated, the commands **Trace.Find** and **Trace.FindAll** are to be used to find the matching items in the trace recording that are fulfilling the complex search criteria as specified by the CTL program.

CTL for trace find does not require any onchip triggering logic. Thus, CTL for trace find has unlimited complexity and can be used with any target providing trace capabilities.

When using **<trace>.Mode STREAM**, it is possible to analyze trace results while streaming using the option **/SPY**:

**Trace.FindAll /SPY**

The search result could be used as a test vehicle for onchip triggers: The trace stream file is processed and analyzed at runtime (while the target is running and the trace is armed) to search for items fulfilling the complex search criteria as specified by the CTL program. The target and/or the trace recording could be stopped (**Break** or **TraceTrigger**) when the scenario of interest is recorded and detected.

Compared to Onchip CTL, CTL for Trace Find has a longer response time. The response time is affected by:

- The processing capacity of the host computer.

- The bandwidth of the whole trace transmission chain (from TRACE32 debug and trace tool to the hard drive of the host computer).

The following table recapitulates the list of the TRACE32 commands that are used for CTL Trace Find.

|                              |                                                                     |

|------------------------------|---------------------------------------------------------------------|

| <b>Trace.FindProgram</b>     | Opens interactive softkey-driven editor for trace find CTL programs |

| <b>Trace.FindReProgram</b>   | Activates existing program file for trace find target               |

| <b>Trace.FindViewProgram</b> | Opens a window that shows the state of the CTL trace find program   |

## CTL Streaming Trace Trigger

---

tbd.

|                        |      |

|------------------------|------|

| <b>RTS.Program</b>     | tbd. |

| <b>RTS.ReProgram</b>   | tbd. |

| <b>RTS.ViewProgram</b> | tbd. |

| <b>RTS.CLEAR</b>       | tbd. |

# CTL for Onchip Triggers Logic

---

To use onchip CTL, the target CPU must provide hardware support to implement complex triggers.

The following subsections are independent. Each is discussing onchip CTL implementation for a specific target architecture. Selected use cases and example CTL programs are presented.

- [CTL for TriCore MCDS](#)

- [CTL for Arm ETM](#)

## Supported Targets

---

Onchip CTL is only supported for AURIX devices with available MCDS modules (MCDS, MCDSlight, or miniMCDS). CTL support for miniMCDS requires TRACE32 release 2023/02 or newer.

The PRACTICE function **MCDS.Module.NAME()** could be used to check the name of the MCDS module for the selected CPU.

## Multicore Support

---

The MCDS module of TriCore devices is restricted to generating trace and trigger information for a limited number of cores. The consequence is that the multicore agents are restricted to the TriCore cores that are assigned to the PowerView instance, and that are selected as core agents via the MCDS window or using the commands **MCDS.ProgramTrace.Aagents** and **MCDS.DataTrace.Aagents**.

## Selective Bus Trace

---

CTL provides a simple interface for selective bus trace. The complex statements are to be assigned to the appropriate bus agents.

- The agent `SPB::` is to be used for tracing and triggering over the System Peripheral Bus (SPB).

- The TriCore MCDS module is using trace multiplexers to select which trace sources are to be observed on the Shared Resource Interconnect (SRI) fabric. SRI agent names are formed by the SRI- prefix, followed by the name of the trace source as defined by Trace Source Multiplexer setting options in the Infineon documentation. Following are some examples:

- `SRI-LMU::` AURIX TC2x agent name to observe access to LMU SRAM and EMEM via SRI.

- `SRI-OLDA::` AURIX TC3x agent name to observe access to Online Data Acquisition via SRI.

- `SRI-DMA::` AURIX TC3x agent name to observe DMA transactions via SRI.

- `SRI-CPU1::` AURIX TC2x/TC3x agent name to observe access to TriCore1 local memories via SRI.

Not all trace sources are available for all target CPUs. The exhaustive list of available bus agents for each CPU selection could be displayed by clicking on the advanced button of the MCDS window.

When activating a CTL program, an automatic configuration of the MCDS trace source multiplexers is performed. TRACE32 combines the list of agents issued from the following configurations and configures the trace source multiplexers accordingly:

- The list of agents that are used by the compiled CTL program.

- The list of core agents that are selected by the commands **MCDS.ProgramTrace.Agents** and **MCDS.DataTrace.Agents**

- The list of bus trace agents that are selected by the command **MCDS.BusTrace.Agents**

- The status of the peripheral trace that is configured by the command **MCDS.PERipheralTrace**

An error is thrown if there is no valid MCDS configuration to observe all the selected agents at the same time. The user must decide which agents are most important to be observed for his use case.

|                                                                                   |                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | When a CTL program is activated, the configuration of the trace source multiplexers performed by the same PowerView instance via the commands <b>MCDS.SOURCE.Set</b> is discarded. |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

## TriCore Data Trace: COREx Vs. SRI-CPUx

---

Using the MCDS module of AURIX devices there are 2 options to observe memory accesses relatively to a TriCore core:

- Observe the read/write accesses performed by the core (e.g. when executing a load or store instruction). In this configuration, the TriCore core is observed as a bus master.

- Observe the read/write accesses to the core local memories via the SRI fabric. In this configuration, the TriCore core is observed as a bus slave incurring the access.

Different CTL agents are to be used in both cases.

### Example:

CORE0 :: is used to observe the first core assigned to the PowerView instance as a master. In this case, memory accesses performed by the core are to be observed.

SRI-CPU0 :: is used to observe TriCore0 as an SRI slave. In this case, accesses to the core local memories via SRI are to be observed. The agents are distinguished by the physical index of the TriCore cores (SRI-CPU1 :: refers to TriCore1, ..., SRI-CPU5 :: refers to TriCore5).

MCDS module of AURIX TC2x allows a selected TriCore to be observed as a core (read/write accesses generated by the core are observed) and SRI slave at the same time. E.g. a CPU source Multiplexer could be configured to observe the core accesses, and a SRI source multiplexer could be configured to observe the same core as SRI slave.

As opposed to AURIX TC2x, MCDS module of AURIX TC3x only allows the core to be observed either as a master or as an SRI slave but not both at the same time. CTL throws an error when a user program causing such a conflict is enabled.

## Limitations

---

- The current implementation of onchip CTL for TriCore doesn't support complex statements that combine conditions and actions issued from different agents.

- `JointCORE:` : agent is currently not supported by onchip CTL for TriCore.

- Due to known behavior of the MCDS module, there is a dead time of up to 2 MCDS clock cycles during counters, flags, and state changes. This must be considered by the user when writing CTL programs or analyzing the test results.

# Examples

In this section, selected CTL use-cases for TriCore MCDS are presented.

## Use case 1: Debug Memory Overwrite

### User Story - Part 1:

In this example, an AURIX TC3x emulation device is used (e.g. TC397XE)

The user expects the variable `vdouble` to be only changed by the function `func2c`. But this gets overwritten by other values than the function `func2c` is expected to write.

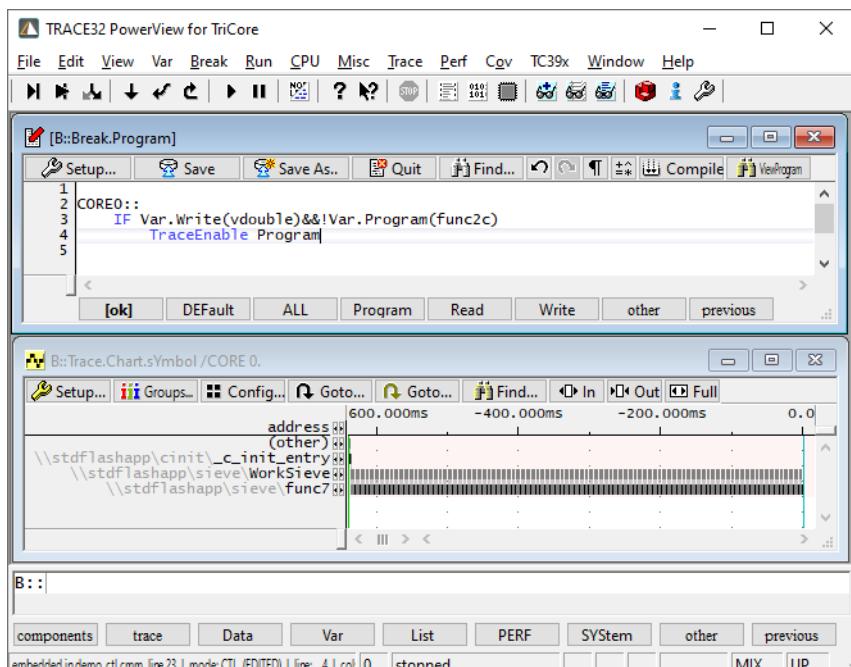

As a first test, the following CTL program is used to check if TriCore0 is performing any write access to `vdouble` from outside the function `func2c`.

### CTL Program:

```

CORE0 ::

IF Var.Write(vdouble)&&!Var.Program(func2c)

TraceEnable Program

```

By prefixing a qualifier with “`Var.`”, the address range of the specified source-level expression is used.

### Results:

The test shows that the startup code `_c_init_entry` and other functions (`WorkSieve` and `func7`) are also writing to `vdouble` (see the trace chart in the following screenshot).

## User Story - Part 2:

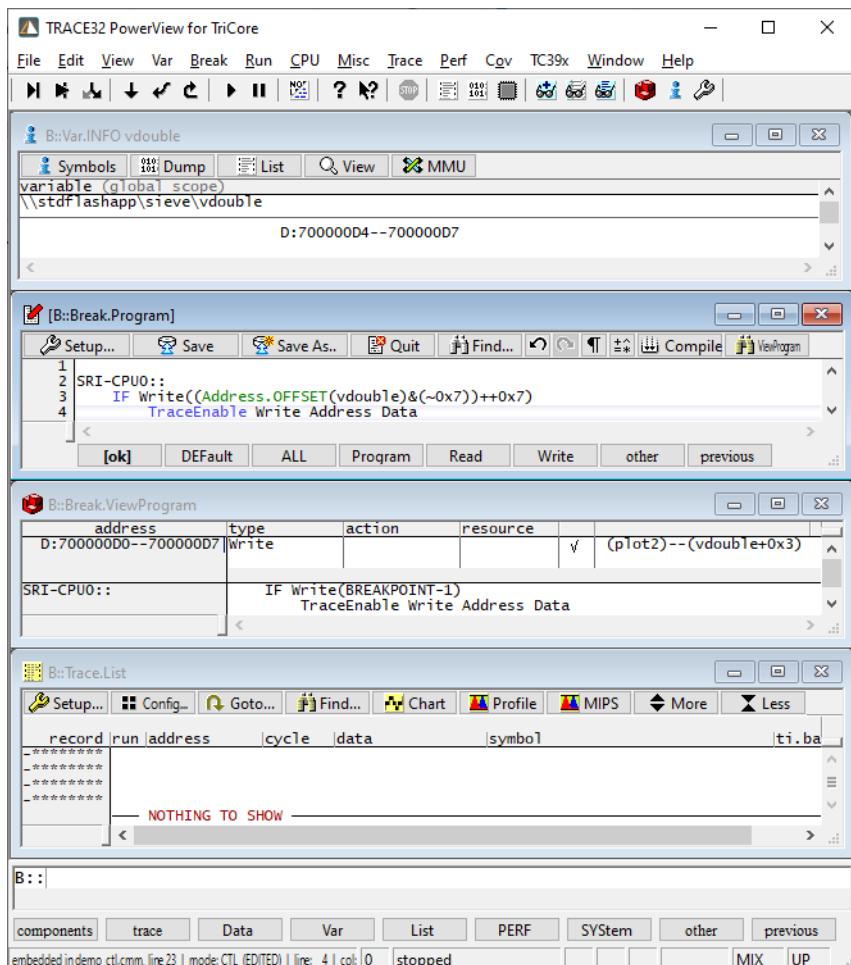

The variable `vdouble` is located in the DSPR of TriCore0. The user requirement is to check that no other TriCore cores or bus agents are also writing to this variable. To achieve this, TriCore0 is to be observed as SRI slave using the agent `SRI-CPU0::`:

Considering that the write access might be part of a 64-bit burst write, the address range needs to be extended to cover a 64-bit aligned range. PRACTICE functions and other arithmetic calculations could be invoked by the CTL program. In this example the PRACTICE function `ADDRESS.OFFSET()` is used to retrieve the variable address in-order to calculate the 64-bit address range to be observed.

### CTL Program:

```

SRI-CPU0:::

IF Write( (Address.OFFSET(vdouble) & (~0x7) ) ++0x7)

TraceEnable Write Address Data

```

### Results:

This second test proves that no other write access to `vdouble` is performed by any agent other than TriCore0: The resulting `Trace.List` window in the following screen shot is empty.

In this example, an AURIX TC3x emulation device is used (e.g. TC397XE)

### **User Story:**

In the used test application the variable `mcount` is incremented each iteration of the function `mainloop`. The user needs to measure the runtime of the function `sieve` which is called once by `mainloop` iteration. Runtime measurement is to be started after a specified number of iterations.

The user requirements for this test case are as follows:

- Trace all write accesses to `mcount` (the address and the write values are to be sampled).

- Starting from the iteration number 20000 of the function `mainloop`, the entry and return instructions of the function `sieve` are to be traced.

- The measurements are to be stopped after collecting 1000 runtime samples.

### **CTL Program:**

CTL flags can be used to implement the test requirements:

```

IF Var.Write(mcount)

TraceEnable Write Address Data

IF Var.Write(mcount==20000.)

SET myFlag

IF (Program(ENTRY:sieve) || Program(RETURN:sieve)) && FLAG(myFlag)

TraceEnable Program

IF Var.Write(mcount==21000.)

Break

```

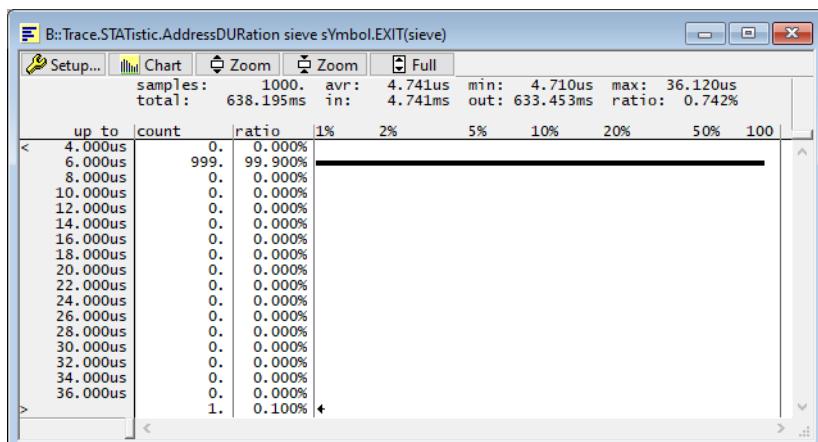

### **Results:**

The **Trace.List** window shows that program trace (for the entry and return instructions of the function `sieve`) is started after the value 20000 (0x4E20) is written to `mcount`.

The window **Trace.STATistic.AddressDURation** shows that 1000 runtime measurements of the function `sieve` are recorded (samples: 1000). In a single iteration, the execution time of `sieve` took longer time (max: 36.12 $\mu$ s) than in usual runs (avr:4.741 $\mu$ s)

### User Story:

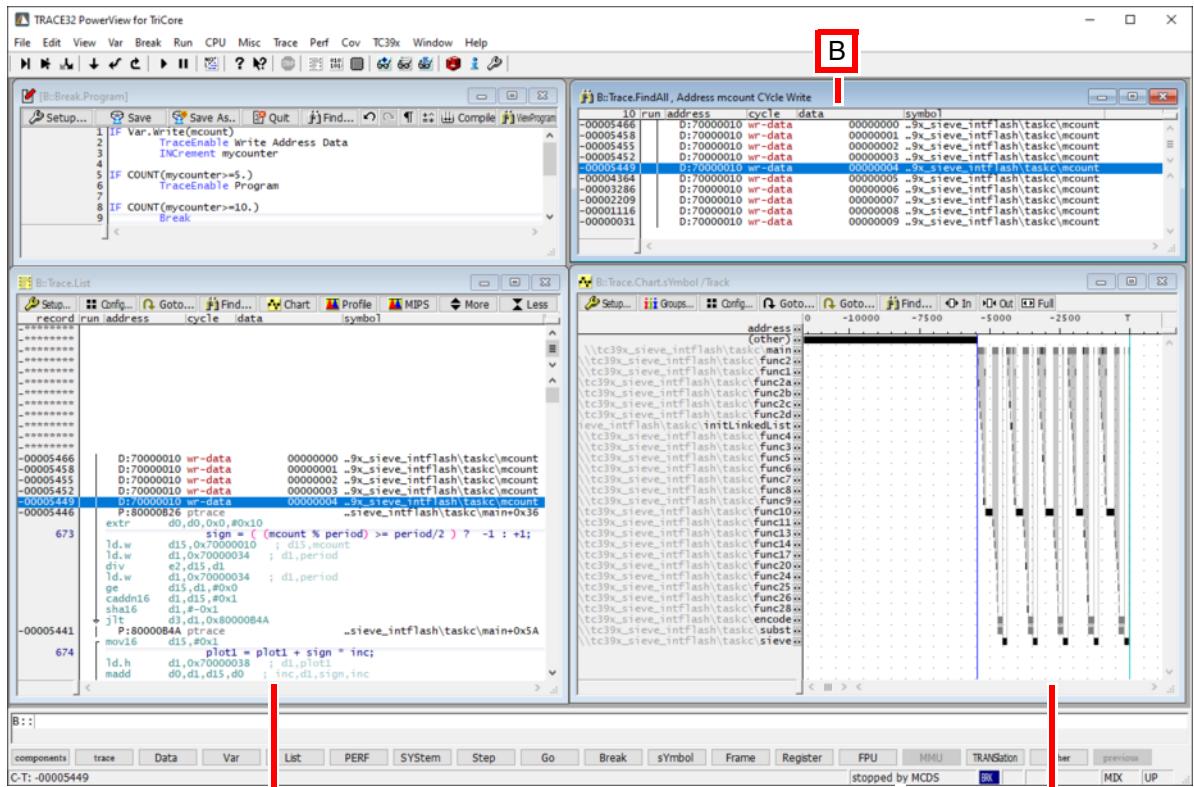

In the used test application the variable `mcount` is incremented each iteration of the `main` loop.

The user needs to start sampling the program flow after a given number of iterations. The user requirements for this test case are as follows:

- Trace all write accesses to `mcount` (the address and the write values are to be sampled).

- Starting from the 5<sup>th</sup> iteration of the `main` loop, the program flow trace is to be enabled.

- The target is to be stopped after the 10<sup>th</sup> iteration of the `main` loop.

### CTL Program:

In the following example program, a CTL counter “`mycounter`” is used to count the number of write access to the variable `mcount`.

```

IF Var.Write(mcount)

TraceEnable Write Address Data

INCrement mycounter

IF COUNT(mycounter>=5.)

TraceEnable Program

IF COUNT(mycounter>=10.)

Break

```

### Results:

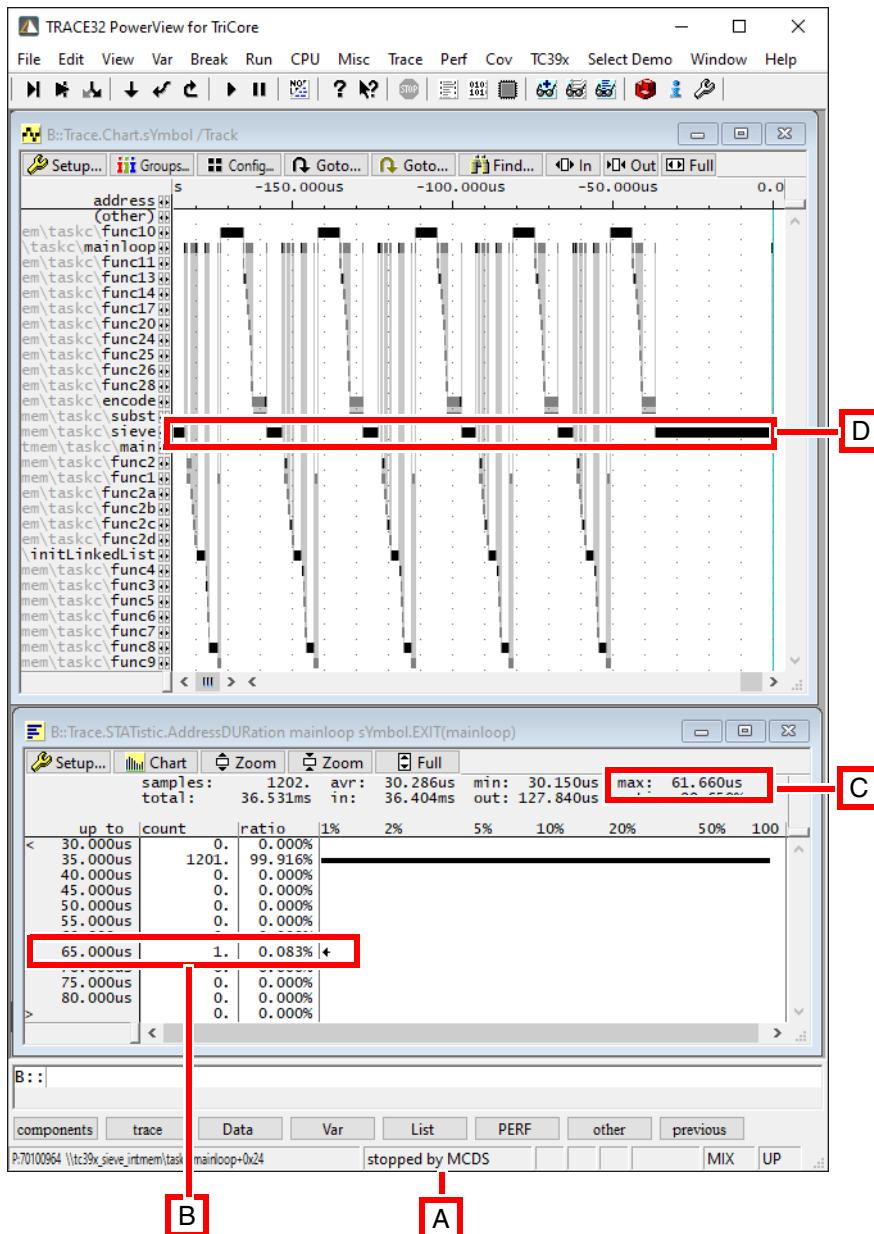

Test results shown in the following screenshot could be interpreted as follows:

- A The status bar shows the state “stopped by MCDS”. This indicates that an MCDS trigger has stopped the target.

- B The trace find window shows that the target executed the main loop for exactly 10 iterations (10 writes to `mcount` are recorded).

- C The trace list window shows that the program flow trace was enabled starting from the 5<sup>th</sup> iteration.

- D The trace chart shows that the program trace was enabled during the last 5 iterations: The leaf function `sieve` which is called once per `main` loop was called exactly 5 times.

---

©1989-2025 Lauterbach

---

Application Note for Complex Trigger Language | 25

### User Story:

In a real-time context, the execution time of the function `mainloop` must not exceed a maximum specified time of 35  $\mu$ s. In rare cases, it happens that the execution time exceeds 60  $\mu$ s.

An AURIX TC3x emulation device is used, but the target board doesn't provide an AGBT interface. Only an onchip trace buffer of 2MBytes is available. The user estimates that, when the error case occurs, the program flow history available in the onchip trace buffer should be enough to track down the issue. The requirements are as follows:

- Unconditional program flow trace must be enabled.

- To track the number of execution loops, all write accesses to the variable `mcount` must be recorded.

- When detecting the error case (i.e. the execution time of the function `mainloop` exceeds a maximum specified duration of 35  $\mu$ s) the trace recording must be kept enabled till the next return of the function `mainloop` is executed.

## CTL Program:

```

-----

// State independent complex statements

-----

// Enable unconditional program flow trace

IF TRUE()

TraceEnable Program

// Sample all write access to mcount

IF Var.Write(mcount)

TraceData

-----

// State Machine implementation to stop

// tracing and Break if the mainloop

// execution time exceeds 35µs.

-----

level0:

IF Program(ENTRY:mainloop)

GOTO level1

level1:

// Restart the timer at entry to level1

IF STATE.ENTER()

RELOAD task_timer

// Keep counting as long as level1 is active

IF TRUE()

ENABLE task_timer

// mainloop return with no timeout detected

// => Go back to level0

IF Program(RETURN:mainloop)

GOTO level0

// A timeout is detected => Go to level3

IF TIME(task_timer)>=35.us)

GOTO level3

level3:

// level3 is only reached if a time-out is detected

// => Stop tracing and break at return of the mainloop

IF Program(RETURN:mainloop)

TraceTrigger

Break

```

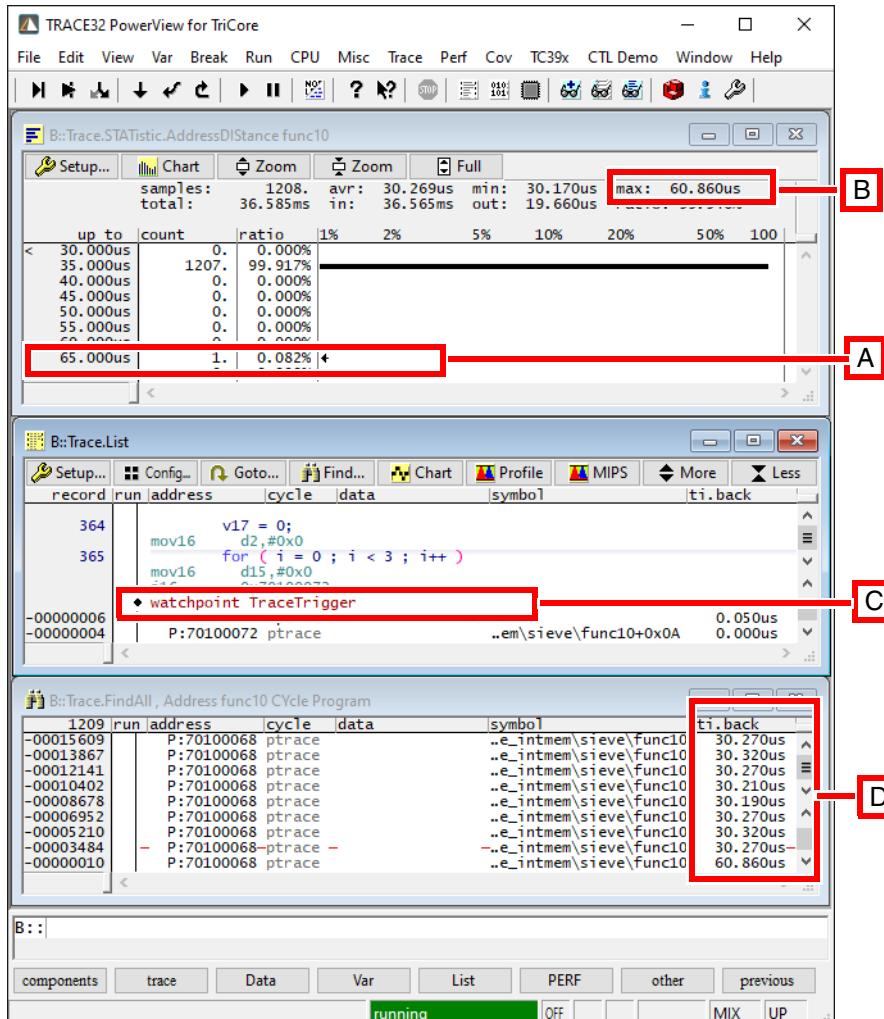

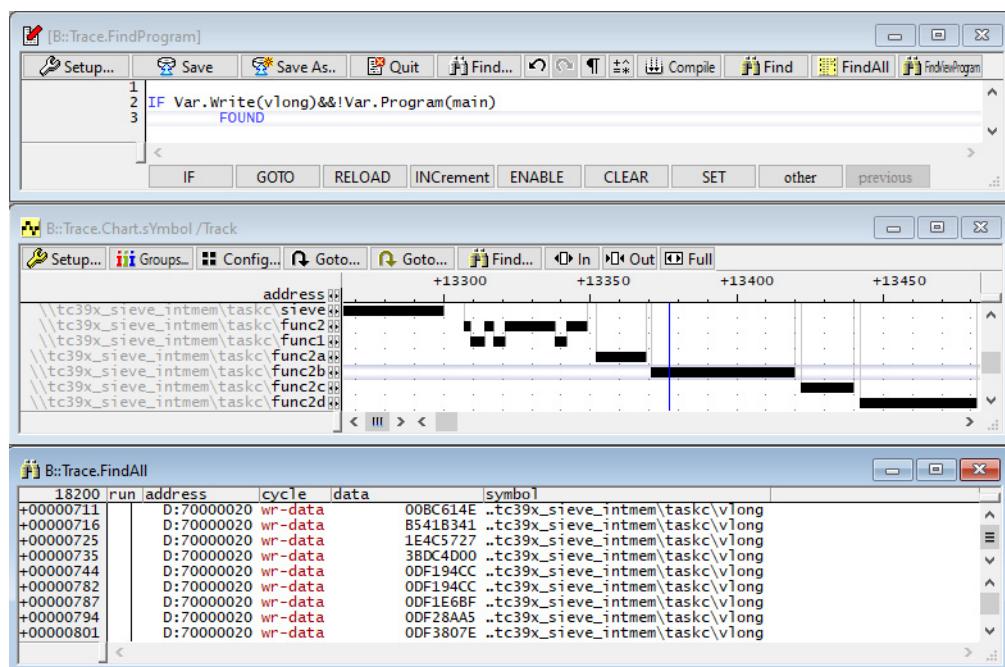

## Results:

- A** The status bar shows the state “stopped by MCDS”. This indicates that an MCDS trigger has stopped the target.

- B** The **Trace.STATistic.AddressDURation** window shows that the execution time of the function `mainloop` has once exceeded the duration of 35  $\mu$ s.

- C** The maximum measured duration of `mainloop` is 61.660  $\mu$ s.

- D** The **Trace.Chart.sYmbol** window shows that the function `sieve` took a longer execution time than the usual runs. The user must examine the program flow trace and focus his analysis on the function `sieve`.

### User Story:

In a real time context, a function `func10` must be called at least once every 35  $\mu$ s. In rare cases, the time distance between 2 consecutive calls exceeds 60  $\mu$ s.

An onchip trace configuration on AURIX TC3x emulation device is used. The user needs to examine the program flow trace when the timing constraint is violated. The requirements are as follows:

- Unconditional program flow must be enabled.

- When the timing constraint is violated, the program flow recording is to be kept enabled until the next call of `func10` is executed.

### CTL Program:

```

// Enable unconditional program flow trace

IF TRUE()

TraceEnable Program

// Set monitoring flag and reload the distance timer at every

// execution of the func10 entry

IF Program(ENTRY:func10)

SET monitoring_flag

RELOAD distance_tmr

// Keep incrementing the distance timer as long as the monitoring

// flag is set

IF FLAG(monitoring_flag)

ENABLE distance_tmr

// Set a time-out flag when the value of the distance monitoring

// timer exceeds 35  $\mu$ s

IF Time(distance_tmr>35.us)

SET timeout_flag

// Stop trace recording at the first execution of func10 entry

// following a time-out

IF FLAG(timeout_flag)&&Program(ENTRY:func10)

TraceTrigger

```

## Results:

- A The **Trace.STATistic.AddressDIStance** window shows that, over 1208 recorded trace samples, the timing constraint is violated once.

- B The maximum recorded time distance between consecutive calls of `func10` is 60.86  $\mu$ s.

- C The watchpoint mark the occurrence of the `TraceTrigger` action

- D The column “ti.back” shows that the distance between the last 2 calls of `func10` exceeds 35  $\mu$ s for the first time.

## Supported Targets

CTL is available exclusively on Arm cores that include an Embedded Trace Macrocell (ETM). To verify if your core under debug supports ETM, use the PRACTICE function [ETM\(\)](#). Execute the following command to check for ETM availability:

```

PRINT ETM()

```

Alternatively, you can use the following PRACTICE script to verify whether you can use CTL with your device:

```

IF ETM()

PRINT "Your device contain ETM and you can use CTL"

ELSE

PRINT "Your device does not contain ETM and you cannot use CTL"

```

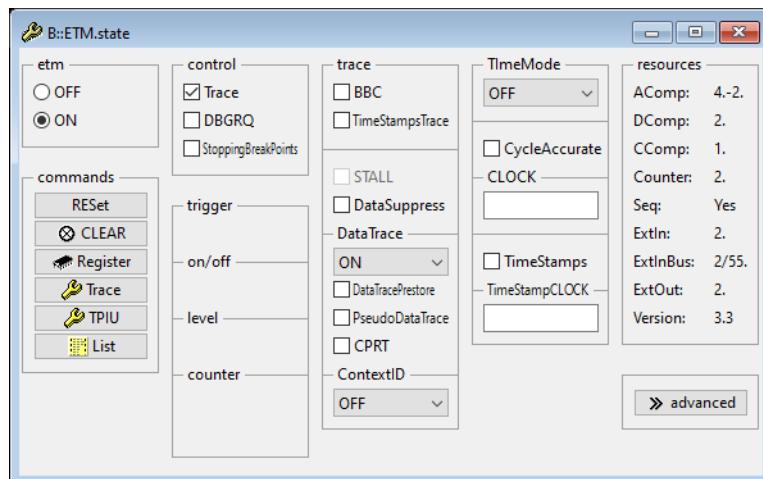

## Limitations

The CTL is fundamentally reliant on the resources of the ETM in your core(s) under debug. For example, if you want to stop program execution when an invalid value is written to a variable, you will need an ETM that offers both address and data value comparators. The [ETM.state](#) window provides a good overview of the available resources.

## Examples

In this section, selected CTL use-cases for Arm ETM are presented.

Used Core: Cortex-R7

ETM Version: ETMv4

The objective is to stop the program execution when the interrupt disable period of the CPU (Cortex-R7) surpasses a certain limit (longer than the specified duration). Essentially, the user aims to determine which driver is responsible for keeping interrupts disabled for too long. The user employs the global functions `local_irq_disable()` and `local_irq_enable()` to manage the disabling and enabling of interrupts. It is necessary to stop the program execution (**BREAK** command) when the interrupt disable period reaches or exceeds 100ms.

### CTL Program:

```

irq_on:

// Start level

// Transition to irq_off state when function local_irq_disable is entered

IF Program(ENTRY:local_irq_disable)

GOTO irq_off

irq_off:

// Transition back to irq_on state when the local_irq_enable function

// returns.

IF Program(RETURN:local_irq_enable)

GOTO irq_on

// Initialize the timer when entering this state

IF STATE.ENTER()

RELOAD timer_irq_off

// Continuously enable the timer while in this state

IF TRUE()

ENABLE timer_irq_off

// Check if the timer has reached or exceeded 100 milliseconds.

IF TIME(timer_irq_off>=100.ms)

Break

```

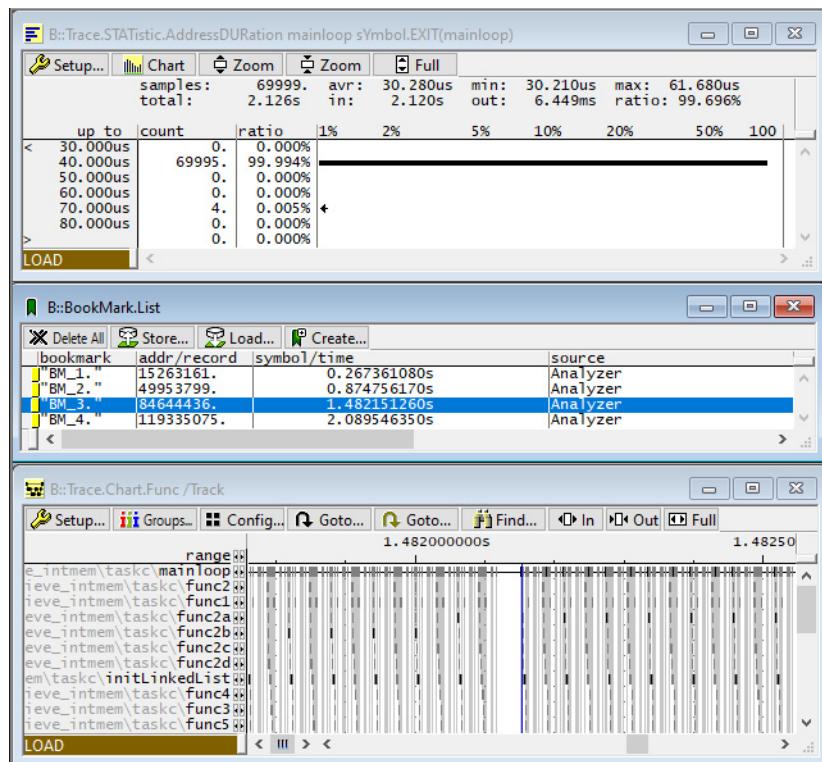

### Result:

The program execution is stopped, and the status bar displays “stopped by ETM” when the interrupt disable period surpasses 100ms.

Used Core: Cortex-R5

ETM version: ETMv3.3

This demo is based on the standard demo application sieve;

```

~/demo/arm/hardware/zynq_ultrascale/ultra96-rev2/ultra96-amp/ultra96-rev2_amp_onchip_etf_trace_sram.cmm

```

The user expects the variable `vdouble` to be modified exclusively by the function `func2c`. However, `vdouble` is being overwritten by values that are not generated within `func2c`.

As an initial test, the following CTL program is used to check whether the program running on the Cortex-R5 core performs any write access to `vdouble` from outside the `func2c` function.

## CTL Program:

```

// Check for any write access to the variable vdouble and

// ensure that the write access does NOT occur within the function func2c

IF Var.Write(vdouble)&&!Var.Program(func2c)

// Advice ETM to generate program trace information

// when both conditions are met

TraceEnable Program

```

## Results:

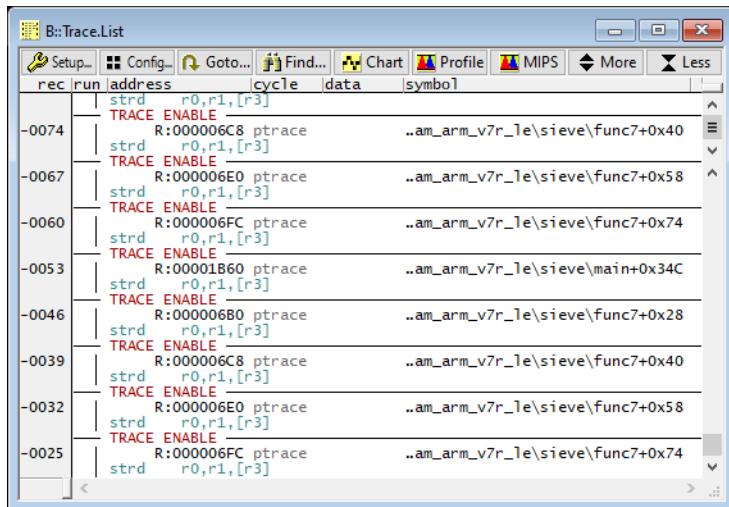

The **Trace.List** window displays the program locations outside the `func2c` function that have written to `vdouble`:

## Use case 3: Stop program execution on instruction cache miss event

Used Core: Cortex-R7

ETM version: ETMv4

The goal of this CTL program is to stop program execution when an instruction cache miss occurs. It leverages the availability of PMU (**BMC** in TRACE32) events as ETM inputs through the extended external input facility. This allows for precise troubleshooting and performance analysis.

The CTL program looks like this:

```

IF BMC (ICMISS)

Break

```

## Result:

The test results show “stopped by ETM” in the status bar immediately after the next instruction cache miss:

**NOTE:**

This applies only when the Arm core is equipped with both **BMC** and **ETM**.

# Examples for CTL Trace Find

## Use case 1: Checking Variable Access

### User Story:

The user needs to find all write access to a variable `vlong` from outside the function `main`.

### Trace Find Program: `vlong_access.ct`

```

IF Var.Write(vlong)&&!Var.Program(main)

FOUND

```

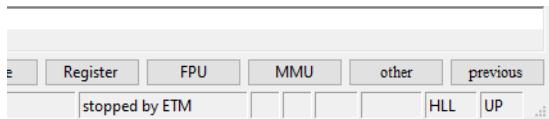

### Results:

The results could be explored using the TRACE32 PowerView:

1. Click on the compile button in the CTL Trace Find editor.

2. Open a trace chart window with the **/Track** option by executing the command **Trace.Chart.sYmbol /Track**

3. Navigate through the matching items using the button **Find**. Each time the trace chart window will be updated; the function that is performing the access is highlighted. Alternatively, the **FindAll** button could be used to list all the matching items in the **Trace.FindAll** window.

A scripting approach could also be used. The following PRACTICE script prints the names of matching items' functions to the message area window.

```

// activate the CTL find program from the file vlong_access.ct

Trace.FindReProgram ~~~~/vlong_access.ct

// search for the first trace record fulfilling the CTL program search

// criteria

Trace.Find

WHILE FOUND()

(

// print the name of the matching item's function to the area window

PRINT sYmbol.FUNCTION(TRACK.ADDRESS.PROG())

// search for the next trace record fulfilling the CTL program search

// criteria

Trace.Find

)

```

## Use case 2: Checking Timing Constraints - Address Duration

---

### User Story:

The user needs to perform post-mortem analysis of a trace recording. The trace is loaded to a TRACE32 Instruction Set Simulator. The user needs to verify that the execution time of the function `mainloop` does not exceed a specified time of 35  $\mu$ s.

### Trace Find Program: `check_address_duration.ct`

```

start_level:

// Detected Entry of the main loop

IF Program(ENTRY:mainloop)

GOTO check_level

check_level:

// Reset the task_timer

IF STATE.ENTER()

RELOAD task_timer

// Enable the task timer as long as check_level is active

IF TRUE()

ENABLE task_timer

// Go back to start_level at Return from the function

// mainloop

IF Program(RETURN:mainloop)

GOTO start_level

// task_timer exceeds 35  $\mu$ s

// => a timeout is detected

IF TIME(task_timer>=35.us)

GOTO timeout_level

timeout_level:

// Search for the next return from mainloop and

// mark it as FOUND and go back to start_level to

// continue the test

IF Program(RETURN:mainloop)

FOUND

GOTO start_level

```

A PRACTICE script could be used to set bookmarks for all the trace records breaking the timing constraint.

## Script:

```

PRIVATE &index

Trace.FindReProgram ~~~~/check_address_duration.ct

BookMark.RESet

&index=1.

// Find the first trace record matching the CTL find program criteria

Trace.Find

WHILE FOUND()

(

// Compose a unique bookmark name

&bookmark="BM_"+"&index"

// Set a bookmark for the FOUND trace record

Trace.Bookmark "&bookmark" TRACK.RECORD()

&index=&index+1.

// Find the next trace record matching the CTL find program criteria

Trace.Find

)

```

## Results:

In this example, the timing constraint was broken four times. These are identified by the bookmarks “BM\_1”, “BM\_2”, “BM\_3”, and “BM\_4”.

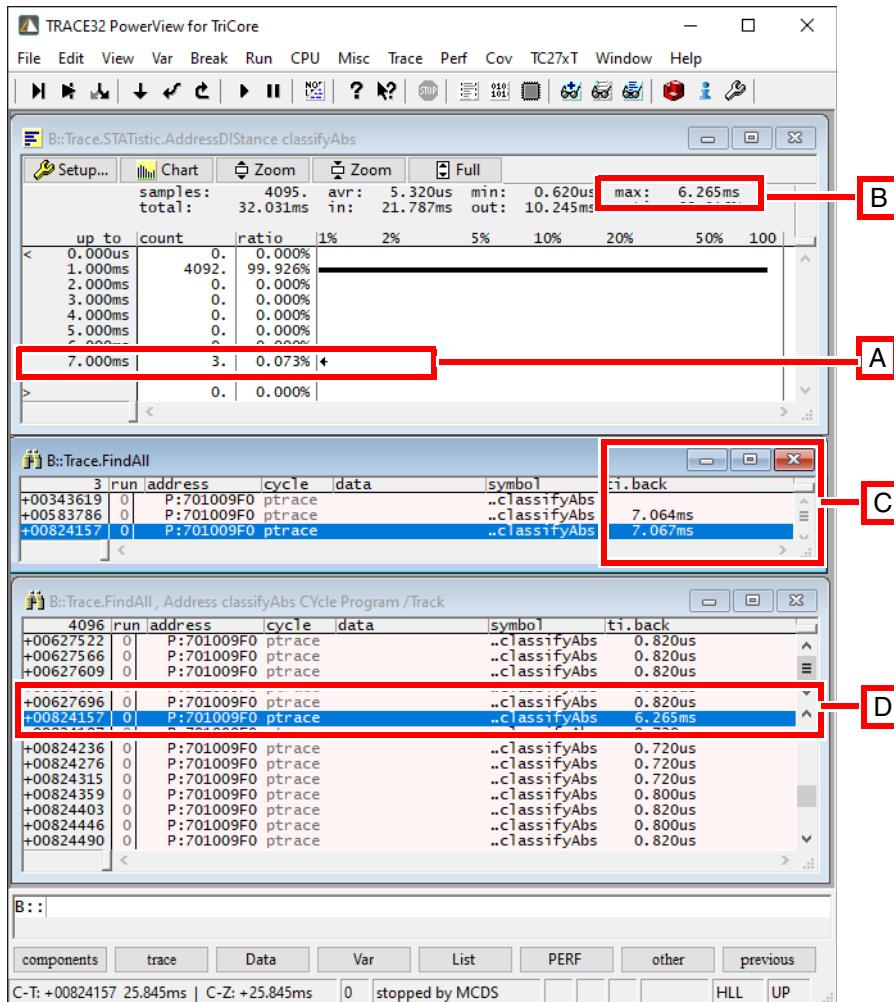

# Use case 3: Checking Timing Constraints - Address Distance

## User Story:

Runtime analysis of the user application program flow using **Trace.STATistic.AddressDIStance** shows that a function `classifyAbs` is called at least once each 1 ms. In some cases (3 times/4095 samples) the time distance between consecutive calls of `classifyAbs` exceeds 6 ms. A trace find program can be used to locate the trace samples where the timing constraint gets violated.

## Trace Find Program: `check_address_distance.ct`

```

// For each trace sample corresponding to the entry of the function

// classifyAbs:

//   + Set a flag "monitoring_flag"

//   + Reload the distance monitoring timer "distance_tmr"

IF Program(ENTRY:classifyAbs)

SET monitoring_flag

RELOAD distance_tmr

// As long as the monitoring flag is set, keep incrementing

// the distance monitoring timer

IF FLAG(monitoring_flag)

ENABLE distance_tmr

// In case the monitoring timer exceeds a limit of 1 ms

//   + The timeout flag is set

//   + The monitoring flag is cleared

//   + The distance timer is reset

IF Time(distance_tmr>1.0ms)

SET timeout_flag

CLEAR monitoring_flag

RELOAD distance_tmr

// The next trace sample representing the entry of the function

// classifyAbs with the timeout flag set is added to the trace find

// results of interest (FOUND)

// The timeout flag is cleared for processing the rest of the trace

// samples

IF Program(ENTRY:classifyAbs)&&FLAG(timeout_flag)

FOUND

CLEAR timeout_flag

```

The trace find program could compiled/activated via the command **Trace.FindReProgram** . Trace samples of interest can be listed using the command **Trace.FindAll** e.g. as follows:

```

// Activate the trace find program

Trace.FindReProgram ~~~~/check_address_distance.ct

// Display the trace find results

Trace.FindAll

```

## Results:

- A** The **Trace.STATistic.AddressDIStance** window shows that, over 4095 recorded trace samples, the timing constraint is violated 3 times.

- B** The maximum recorded time distance between consecutive calls of `classifyAbs` is 6.265 ms.

- C** The time displayed in `ti.back` column of **Trace.FindAll** window is not corresponding to the time distance between 2 consecutive calls of `classifyAbs`. Actually, this represents the time distance between 2 samples of `classifyAbs` violating the timing constraint.

- D** The window **Trace.FindAll, Address classifyAbs CYcle Program /Track** is to be used to examine the maximum time distance between 2 consecutive calls of `classifyAbs`

# Keyword Reference: CTL Conditions/Triggers

---

## BREAKPOINT

ABCDE breakpoint

Format: **BREAKPOINT (<type>)**

<type>: **Alpha | Beta | Charly | Echo**

## BusTrigger

Incoming trigger signal

Format: **BusTrigger (<channel>)**

## BMC

Benchmark counter event

Format: **BMC (<event>)**

This condition is only supported if the target processor provides an Embedded Trace Macrocell (ETM) and BenchMark Counters. Refer to the corresponding [“Processor Architecture Manuals”](#).

### Example:

```

IF BMC(dcachemiss)

INCrement counter1

```

## COUNT

Trigger on event counter

Format: **COUNT (<name/count>)**

Format: **CLOCKS (<name/count>)**

## Example:

Enable program trace for 100 clock cycles starting from the execution of the first instruction of the `sieve` function.

```

start:

IF Program(ENTRY:sieve)

GOTO level1

level1:

// Reset the clock counter at state change to level1

IF STATE.ENTER()

RELOAD clock_counter

// Enable Program trace and clock_counter as long as

// level1 is active

IF TRUE()

TraceEnable Program

ENABLE clock_counter

// Stop tracing when the clock_counter reach the limit of 100 cycles

IF CLOCKS(clock_counter>=100.)

TraceTrigger

```

# CTM

# Cross trigger

Format: **CTM (<channel>)**

This condition is only supported if the target processor provides an Embedded Trace Macrocell (ETM) and a CoreSight Trigger Matrix (CTM).

# EXTIN

# External input

Format: **EXTIN (<channel>)**

This condition is only supported if the target processor provides an Embedded Trace Macrocell (ETM).

Format: **FALSE ()**

## FLAG

Flag status

Format: **FLAG (<name/value>)**

### Example:

Enable program trace for the address range of the function `sieve` if the variable `mstatic1` has a value of 2:

```

IF Var.Write(mstatic1==2)

SET myflag

IF Var.Write(mstatic1!=2)

CLEAR myflag

IF Var.Program(sieve)&&FLAG(myflag)

TraceEnable Program

```

## MACHINE

Machine comparator

Format: **MACHINE (<machine>)**

This condition is only supported if the target processor provides an Embedded Trace Macrocell (ETM) and hypervisor extensions. Once the Hypervisor Awareness is configured in TRACE32, you can perform comparisons on specific machine within your CTL program.

### Example: selective trace on a specific machine in hypervisor setup

```

IF MACHINE( "FreeRTOS" )

TraceEnable Program

```

**NOTE:** The command **Break.CONFIG.UseMachineID ON** should be set

Format: **Program** (*<item>*)

*<item>*: [*<logical\_operator>*] [**ENTRY**: | **RETURN**: | **RANGE**:] *<addr/data>*

*<logical\_operator>*: ~ | == | != | < | <= | >= | >

**ENTRY**: Address of the function entry point.

**RETURN**: Address of the function exit (function epilogue)

**RANGE**: Function address range

If nothing is specified in front of a function name, ENTRY is default.

## Example:

```

IF Program(ENTRY:sieve)

TraceON Program

IF Program(RETURN:sieve)

TraceOFF Program

```

# ProgramFail

# Conditional instruction execution

Format: **ProgramFail** (*<item>*)

*<item>*: [*<logical\_operator>*] [**ENTRY**: | **RETURN**: | **RANGE**:] *<addr/data>*

*<logical\_operator>*: ~ | == | != | < | <= | >= | >

Format: **ProgramPass (<item>)**

<item>: [*<logical\_operator>*] [**ENTRY:** | **RETURN:** | **RANGE:**] <addr/data>

<logical\_operator>: ~ | == | != | < | <= | >= | >

## Read

Read access

Format: **Read (<item>)**

<item>: [*<logical\_operator>*] <addr/data>

<logical\_operator>: ~ | == | != | < | <= | >= | >

### Example:

```

IF Read(flags)

TraceEnable ALL

```

Format: **ReadWrite** (*<item>*)

*<item>*: [*<logical\_operator>*] *<addr/data>*

*<logical\_operator>*:

~ | == | != | < | <= | >= | >

### Example 1:

```

IF ReadWrite(mstatic1)

TraceData DEFault

```

### Example 2:

```

IF ReadWrite(vint==1000)

SET myFlag

IF FLAG(myFlag)&&Program(ENTRY:sieve)

Break

```

The SingleShot conditions are only supported if the target processor provides an Embedded Trace Macrocell with a single shot comparator (e.g. ETMv4).

## SingleShot.Program

## Single shot program execution

Format: **SingleShot.Program** (*<item>*)

*<item>*: [*<logical\_operator>*] [**ENTRY**: | **RETURN**: | **RANGE**:] *<addr/data>*

*<logical\_operator>*: ~ | == | != | < | <= | >= | >

### Example:

```

IF SingleShot.Program(ENTRY:sieve)

TraceEnable Program

```

## SingleShot.ProgramFail

## Single shot conditional execution

Format: **SingleShot.ProgramFail** (*<item>*)

*<item>*: [*<logical\_operator>*] [**ENTRY**: | **RETURN**: | **RANGE**:] *<addr/data>*

*<logical\_operator>*: ~ | == | != | < | <= | >= | >

Format: **SingleShot.ProgramPass** (*<item>*)

*<item>*: [*<logical\_operator>*] [**ENTRY**: | **RETURN**: | **RANGE**:] *<addr/data>*

*<logical\_operator>*: ~ | == | != | < | <= | >= | >

## SingleShot.Read

## Single shot read access

Format: **SingleShot.Read** (*<item>*)

*<item>*: [*<logical\_operator>*] *<addr/data>*

*<logical\_operator>*: ~ | == | != | < | <= | >= | >

### Example:

```

IF SingleShot.Read(mstatic1)

TraceData Read Address Data

```

Format: **SingleShot.ReadWrite (<item>)**

<item>: [*<logical\_operator>*] <addr/data>

<logical\_operator>: ~ | == | != | < | <= | >= | >

### Example:

```

IF SingleShot.ReadWrite(mstatic1)

TraceData DEFault

```

Format: **SingleShot.Write (<item>)**

<item>: [*<logical\_operator>*] <addr/data>

<logical\_operator>: ~ | == | != | < | <= | >= | >

### Example:

```

IF SingleShot.Write(flags)

TraceEnable ALL

```

The NoSingleShot conditions are only supported if the target processor provides an Embedded Trace Macrocell with a single shot comparator (e.g. ETMv4).

### NoSingleShot.Program

### Non single shot program execution

Format: **NoSingleShot.Program (<item>)**

<item>: [*<logical\_operator>*] [**ENTRY:** | **RETURN:** | **RANGE:**] <addr/data>

<logical\_operator>: ~ | == | != | < | <= | >= | >

#### Example:

```

IF NoSingleShot.Program(ENTRY:sieve)

TraceEnable Program

```

### NoSingleShot.ProgramFail

### Non single shot conditional execution

Format: **NoSingleShot.ProgramFail (<item>)**

<item>: [*<logical\_operator>*] [**ENTRY:** | **RETURN:** | **RANGE:**] <addr/data>

<logical\_operator>: ~ | == | != | < | <= | >= | >

Format: **NoSingleShot.ProgramPass (<item>)**

<item>: [*<logical\_operator>*] [**ENTRY:** | **RETURN:** | **RANGE:**] <addr/data>

<logical\_operator>: ~ | == | != | < | <= | >= | >

Format: **NoSingleShot.Read (<item>)**

<item>: [*<logical\_operator>*] <addr/data>

<logical\_operator>: ~ | == | != | < | <= | >= | >

Format: **NoSingleShot.ReadWrite (<item>)**

<item>: [*<logical\_operator>*] <addr/data>

<logical\_operator>: ~ | == | != | < | <= | >= | >

Format: **NoSingleShot.Write (<item>)**

<item>: [*<logical\_operator>*] <addr/data>

<logical\_operator>: ~ | == | != | < | <= | >= | >

Format: **STATE.LEAVE ()**

**Example:**

```

start:

IF Program(ENTRY:sieve)

GOTO level1

IF STATE.LEAVE()

RELOAD blink_counter

level1:

IF Program(RETURN:sieve)

GOTO start

IF Program(ENTRY:Blink)

INCrement blink_counter

IF COUNT(blink_counter>2)

Break

```

Format: **STATE.ENTER ()**

**Example:**

```

start:

IF Program(ENTRY:sieve)

GOTO level1

level1:

IF STATE.ENTER()

RELOAD blink_counter

IF Program(RETURN:sieve)

GOTO start

IF Program(ENTRY:Blink)

INCrement blink_counter

IF COUNT(blink_counter>2)

Break

```

Format: **STATE.TRACEON ()**

This condition is only supported if the target processor provides an Embedded Trace Macrocell (ETM) versions older than ETMv4.

## TASK

Task comparator

Format: **TASK (<task>)**

This condition is only supported if the target processor provides an Embedded Trace Macrocell (ETM).

Once awareness is configured, you can perform comparisons on specific tasks within your CTL program.

### Example: Selective trace on specific task

```

If TASK("sieve")

TraceEnable Program

```

Format: **TIME (<name/time>)**

**Example:**

```

start:

IF Program(ENTRY:sieve)

GOTO level1

level1:

IF ENTRY()

RELOAD sievetimer

TraceON Program

IF TRUE()

ENABLE sievetimer

IF Program(RETURN:sieve)

TraceOFF Program

GOTO start

IF TIME(sievetimer>200.us)

Break

```

**TRUE**

Always condition

Format: **TRUE ()**

**Example:**

```

start:

IF Program(ENTRY:sieve)

GOTO level1

level1:

IF TRUE()

TraceEnable Program

IF Program(RETURN:sieve)

GOTO start

```

**Var** prefix allows to specify the source-level expression in the syntax of the used programming language (e.g. C, C++).

Then condition will consider the full function/variable range.

## Var.Program

Flat function execution

Format: **Var.Program (<item>)**

<item>: [*<logical\_operator>*] [**ENTRY:** | **RETURN:** | **RANGE:**] <var/data>

<logical\_operator>: ~ | == | != | < | <= | >= | >

### Example:

```

// Trace all write access when executing instructions in the sieve

// function address range

IF Var.Program(sieve)

TraceData Write Address Data

```

## Var.Read

Variable read access

Format: **Var.Read (<item>)**

<item>: [*<logical\_operator>*] <var/data>

<logical\_operator>: ~ | == | != | < | <= | >= | >

Format: **Var.ReadWrite (<item>)**

<item>: [*<logical\_operator>*] <var/data>

<logical\_operator>: ~ | == | != | < | <= | >= | >

## Var.status

tbd.

Format: **Var.status (<item>)**

<item>: [*<logical\_operator>*] <var>

<logical\_operator>: ~ | == | != | < | <= | >= | >

## Var.Write

Variable write access

Format: **Var.Write (<item>)**

<item>: [*<logical\_operator>*] <var/data>

<logical\_operator>: ~ | == | != | < | <= | >= | >

### Example:

```

IF Var.Write(vint==1000)

SET myflag

```

Format: **Write (<item>)**

<item>: [*<logical\_operator>*] <addr/data>

<logical\_operator>: ~ | == | != | < | <= | >= | >

### Example:

```

IF Write(0x70001000!=0x55)

TraceEnable ALL

```

## ZONE

## Zone comparator

Format: **ZONE (<zone>)**

This condition is only supported if target processor provides an Embedded Trace Macrocell (ETM).

# Keyword Reference: CTL Actions

---

## Break

Stop the program execution

---

|         |              |

|---------|--------------|

| Format: | <b>Break</b> |

|---------|--------------|

### Example:

```

// Stop if any write access to mstatic1 is generated by an instruction

// from outside the sieve function range

IF var.Write(mstatic1)&&!Var.Program(sieve)

Break

```

## BusCLOCKS

tbd.

---

|         |                            |

|---------|----------------------------|

| Format: | <b>BusCLOCKS</b> <counter> |

|---------|----------------------------|

## BusCount

tbd.

---

|         |                           |

|---------|---------------------------|

| Format: | <b>BusCount</b> <counter> |

|---------|---------------------------|

## BusTIME

tbd.

---

|         |                          |

|---------|--------------------------|

| Format: | <b>BusTIME</b> <counter> |

|---------|--------------------------|

Format: **BusTrigger [DEFault | 0 | 1]**

This action is only supported if the target processor provides an Embedded Trace Macrocell (ETM) and a CoreSight Trigger Matrix (CTM).

**DEFault** tbd.

**0** tbd.

**1** tbd.

## CLEAR

Clear flag

Format: **CLEAR <flag>**

### Example:

```

IF Program(ENTRY:sieve)

SET flag_sieve

IF Program(RETURN:sieve)

CLEAR flag_sieve

IF Var.Write(mstatic1)&&!FLAG(flag_sieve)

TRACEENABLE Program Write Address Data

```

## CTM

Cross trigger

Format: **CTM [0 | 1 | 2 | 3]**

This condition is only supported if the target processor provides an Embedded Trace Macrocell (ETM) and a CoreSight Trigger Matrix (CTM).

|          |      |

|----------|------|

| <b>0</b> | tbd. |

| <b>1</b> | tbd. |

| <b>2</b> | tbd. |

| <b>3</b> | tbd. |

## ENABLE

Enable counter

Format: **ENABLE** <counter> | <timer>

Enable counting while the condition is verified.

**Example:**

```

IF Program(ENTRY:sieve)

SET flag_sieve

IF Program(RETURN:sieve)

CLEAR flag_sieve

IF FLAG(flag_sieve)

ENABLE timer_sieve

TRACEENABLE Program

IF TIME(timer_sieve>10.us)

TraceTrigger

```

## EVENT

Trace event

Format: **EVENT** [0 | 1 | 2 | 3]

Format: **EXTOUT [0 | 1 | 2 | 3]**

**0** tbd.

**1** tbd.

**2** tbd.

**3** tbd.

## FOUND

Add the trace sample to the search items result

Format: **FOUND**

**Example:**

```

IF Program(ENTRY:sieve)

FOUND

```

## GOTO

Change active state

Format: **GOTO <state>**

**Example:**

```

start:

IF Program(ENTRY:sieve)

GOTO level1

level1:

IF Program(RETURN:sieve)

GOTO start

IF Var.Write(mstatic1)

TraceData Write Address Data

```

Format

**INCrement** <counter>**Example:**

```

IF Program(ENTRY:sieve)

INCrement sieve_cnt

TraceEnable Program

IF COUNT(sieve_cnt==10.)

Break

```

**RELOAD**Reload counter

---

Format

**RELOAD** <counter>**Example:**

```

start:

IF Program(ENTRY:sieve)

GOTO level1

level1:

IF Program(RETURN:sieve)

GOTO start

IF Program(ENTRY:Blink)

INCrement blink_counter

IF STATE.ENTER()

RELOAD blink_counter

IF COUNT(blink_counter>2)

Break

```

Format

**SET** <*flag*>**Example:**

```

IF Var.Write(mstatic1)

Set myflag

IF Program(ENTRY:sieve)&&FLAG(myflag)

Break

```

**Spot**

Shortly stop the program execution

Format

**Spot****Example:**

```

IF Program(ENTRY:sieve)

Spot

```

|        |                                                                        |

|--------|------------------------------------------------------------------------|

| Format | <b>TraceData [DEFault   Read   Write   ReadWrite   Address   Data]</b> |

|--------|------------------------------------------------------------------------|

|                  |                                          |

|------------------|------------------------------------------|

| <b>DEFault</b>   | Is equivalent to ReadWrite Address Data. |

| <b>Read</b>      | Sample read cycles.                      |

| <b>Write</b>     | Sample write cycles.                     |

| <b>ReadWrite</b> | Sample read and write cycles.            |

| <b>Address</b>   | Sample cycle address.                    |

| <b>Data</b>      | Sample cycle data.                       |

**NOTE:** **TraceData [Read | Write | ReadWrite]** without specifying Address or Data will sample cycle address and data.

#### Example:

```

// Trace all the write cycles that are performed by the instructions

// in the address range of the function sieve

IF Var.Program(sieve)

TraceData Write Address Data

```

By using the action TraceData, the status of unconditional program trace is not changed. E.g. if unconditional program trace is enabled, the resulting trace recording will contain unconditional program trace additionally to the selective data trace for the specified events.

Format            **TraceEnable** <parameter>

<parameter>:    [DEFault | ALL | Program | Read | Write | ReadWrite | Address | Data]

|                  |                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------|

| <b>DEFault</b>   | Sample the event depending on the condition. e.g. if the condition is a program condition the program cycles are sampled. |

| <b>ALL</b>       | Sample program, read, and write cycles. For the read and write cycles, the sample address and data are included.          |

| <b>Program</b>   | Sample program cycles.                                                                                                    |

| <b>Read</b>      | Sample read cycles.                                                                                                       |

| <b>Write</b>     | Sample write cycles.                                                                                                      |

| <b>ReadWrite</b> | Sample read and write cycles.                                                                                             |

| <b>Address</b>   | Sample cycle address.                                                                                                     |

| <b>Data</b>      | Sample cycle data.                                                                                                        |

**NOTE:**    **TraceEnable [Read | Write | ReadWrite]** without specifying Address or Data will sample cycle address and data.

### Example 1:

```

// Trace program and all the write cycles that are performed by the

// instructions in the address range of the function sieve

IF Var.Program(sieve)

TraceEnable Program Write Address Data

```

### Example 2:

```

// Trace all the write cycles to mstatic1

IF Var.Write(mstatic1)

TraceEnable DEFault

```

Format      **TraceOFF** <*parameter*>

<*parameter*>:      [DEFault | ALL | Program | Read | Write | ReadWrite | Address | Data]

**DEFault**      tbd.

**ALL**      Switch off sampling program, read, and write cycles.

**Program**      Switch off sampling program cycles.

**Read**      Switch off sampling read cycles.

**Write**      Switch off sampling write cycles.

**ReadWrite**      Switch off sampling read and write cycles.

**Address**      Switch off sampling cycle address.

**Data**      Switch off sampling cycle data.

|        |                            |

|--------|----------------------------|

| Format | <b>TraceON</b> <parameter> |

|--------|----------------------------|

|              |                                                                                                                                 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------|

| <parameter>: | [ <b>DEFault</b>   <b>ALL</b>   <b>Program</b>   <b>Read</b>   <b>Write</b>   <b>ReadWrite</b>   <b>Address</b>   <b>Data</b> ] |

|--------------|---------------------------------------------------------------------------------------------------------------------------------|

|                |      |

|----------------|------|

| <b>DEFault</b> | tbd. |

|----------------|------|