# TRACE 32°

# FASTEST DEBUG & TRACE for Arm® Cortex®-M

# Fastest Debug and Trace for Arm® Cortex®-M

µTrace<sup>®</sup> is Lauterbach's cost-effective all-in-one solution that provides the full feature set for Cortex-M microcontrollers implementing a compact trace port of up to 4 bits.

$\mu$ Trace<sup>®</sup> provides the same features that Lauterbach's industry leading high-end products are known for: highest quality, exceptional functionality and superior support. In addition to its leading debug capabilities in the Cortex-M market,  $\mu$ Trace<sup>®</sup> can capture real-time information like system traces and parallel ETM flow traces, enabling e.g. code coverage and code profiling.

µTrace<sup>®</sup> supports data rates up to 400 Mbit/s per trace line from the CoreSight<sup>™</sup> Trace Port Interface Unit (TPIU). This is 30% faster than competing trace products for Cortex-M based embedded systems. To ensure proper sampling at these speeds, the AutoFocus eye-finder automatically detects the perfect sampling point for each trace line.

### µTrace<sup>®</sup> Characteristics

- Highest performance in the industry for Cortex-M (400 Mbit/s per trace line)

- Leading debug capabilities in the Cortex-M market

- Support for more than 7.000 different Cortex-M based chips

- > USB 3 interface to the host computer

- Support for standard JTAG, Serial Wire Debug (SWD), and cJTAG (IEEE 1149.7)

- > 256 MByte trace memory

- 10-/20-pin half-size connector for target hardware and a wide variety of adapters to work with other connectors

- Voltage range 1.2 to 5.0 V

## Debug Features

- C/C++ debugging

- > Simple and complex breakpoints

- > Read and write memory during program runs

- Flash programming support for FLASH memory on microcontrollers and external flash on the target system.

- Support for Armv8-M security extension (TrustZone<sup>®</sup>)

- OS-aware debugging: µTrace<sup>®</sup> allows for full-stack debugging of your target's operation system together with all tasks. The TRACE32 PowerView UI allows easy access to task lists and other OS specific information.

#### Selection of Supported Chip Families

| Ambiq Micro          | Apollo                                                                          |

|----------------------|---------------------------------------------------------------------------------|

| AMD                  | Xilinx Artix-7                                                                  |

| Analog Devices       | ADuCM3, ADSP-CM4,<br>MAX326xx                                                   |

| Arduino              | Nicla Vision, Nano 33 BLE,<br>Portenta H7                                       |

| GigaDevice           | GD32                                                                            |

| Infineon             | XMC1000/4000/7000, TLE98x,<br>FM3, FM4, PSoC 4/5/6, Traveo II                   |

| Marvell              | 88Q5xxx, 88Q6xxx                                                                |

| Microchip            | SmartFusion, SmartFusion2,<br>ATSAM, PIC32                                      |

| Nordic Semiconductor | nRF51, nRF52, nRF53, nRF91                                                      |

| Nuvoton              | NuMicro                                                                         |

| NXP                  | LPC8xx, LPC1xxx, Kinetis,<br>JN518x, S32K, LPC4xxx,<br>LPC5xxx, i.MX RT, QN90xx |

| onsemi               | LC823450, RSL10                                                                 |

| Raspberry Pi         | RP2040                                                                          |

| Renesas              | RZ/G2L, DA14xxx, RA,<br>R-IN32xx, ZSSC1856                                      |

| Samsung              | S3F                                                                             |

| Silicon Labs         | EFM32, EFR32, EM35                                                              |

| Socionext            | SC1721/1722/1723                                                                |

| ST Microelectronics  | STM32, Teseo V                                                                  |

| Texas Instruments    | Tiva C, Concerto, CC25xx,<br>CC26xx, C32xx, MSP432                              |

| Toshiba              | TX00, TX03, TX04, TXZ4                                                          |

|                      |                                                                                 |

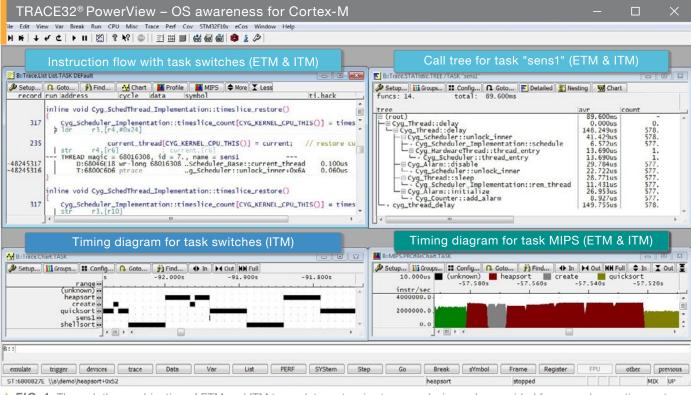

FIG. 1: Through the combination of ETM and ITM trace data, extensive trace analysis can be provided for several operating systems.

## Trace Features

- Support of program-flow traces created by the ETM

- Support of data and event-traces created by the ITM or ETMv4.x

- Off-chip trace of ETM/ITM via TPIU in continuous mode with up to 4 trace pins for detailed analysis

- Off-chip trace of ITM via Serial Wire Output (SWO) for SoCs without TPIU

- On-chip trace of ETM/ITM via ETB (if available) for SoCs without TPIU

- On-chip trace of program-flow via MTB for SoCs without ETM

- Combining of ETM and ITM trace data for a seamless integration of read/write accesses into the instruction flow

- OS-aware tracing

- Analysis of task and function run times

- Trace the execution state of all branch and non-branch instructions

- Code coverage analysis

- On-the-fly transferring of trace data to the host computer

- Energy measurement using optional TRACE32<sup>®</sup> Mixed-Signal Probe

- Concurrent recording of 12 digital signals with optional TRACE32<sup>®</sup> Mixed-Signal Probe

## Combining ETM and ITM Trace Data

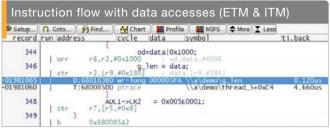

The ETM generates information about the instructions that have been executed. The ITM generates information about the read/write accesses assisted by the Data Watchpoint and Trace unit (DWT).

The ITM trace packets for read/write accesses contain the following information: data address, data value, program counter. Through analysis of the program counter, these separately generated data accesses can be seamlessly integrated into the instruction flow (*figure 2*). This in turn leads to significantly faster error location. The cause of an error such as an incorrect data value being written to an address can be found easily if the write accesses are embedded into the overall instruction flow.

▲ **FIG. 2:** By combining ETM and ITM trace data, read/write accesses can be integrated seamlessly into the instruction flow.

#### OS-Aware Tracing

If an operating system is running, task switch information becomes essential for the trace analysis.

The ITM can generate trace information for each task-switch. Therefore it emits a data-trace message whenever the kernel writes on the variable indicating the active task.

As described on the previous page, data-trace messages can be integrated seamlessly into the instruction flow trace. As a result the task switch information is also integrated into the instruction trace. This improves the readability of the trace listing. The integration of the task switch into the instruction flow trace also forms the basis for the run-time analysis as shown in figure 1.

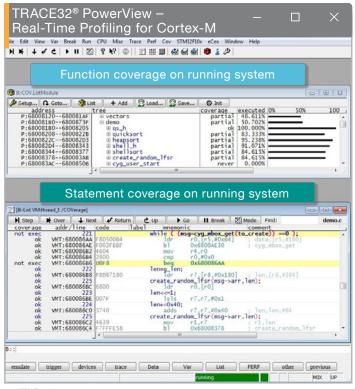

▲ FIG. 3: Real-time Profiling enables code coverage analysis to be followed live on the screen.

#### Recording Modes

To record the trace information generated by the ETM and ITM,  $\mu Trace^{\circledast}$  supports various modes:

#### > FIFO AND STACK MODE

The complete trace information is stored inside the 256 MByte memory of the TRACE32<sup>®</sup> µTrace<sup>®</sup>.

#### STREAM MODE

The complete trace information is streamed to the host computer and stored in a file on its hard-disk.

#### REAL-TIME PROFILING

The trace information relevant for the selected profiling is streamed to the host computer and analyzed during runtime.

Each recording mode has its specific strengths.

**FIFO and STACK Mode** are the most commonly used modes. In STACK mode trace recording stops when the trace memory is full. FIFO mode overwrites the trace memory until the recording stops. The trace analysis is then undertaken after recording is completed. These modes work quickly (200 MByte/s) and are sufficient for error location and run-time analysis.

**STREAM Mode** can collect trace data for a long time period. This is helpful if an error location cannot be triggered, if documentation of a program run is required over a long time or if you want to perform a statistical analysis over a longer period. In stream mode µTrace<sup>®</sup> supports an average trace-rate of 140 MByte/s with temporary peaks up to 200 MByte/s.

**Real-time Profiling** is particularly suitable for performing object statement and object branch coverage. The coverage analysis can be followed live on the screen and the test results are visible immediately (see *Figure 3*). Lines marked as "ok" have already been covered, lines marked as "not exec" may require additional test stimuli.

#### FOR MORE INFORMATION VISIT: www.lauterbach.com/microtrace www.lauterbach.com/os-awareness

# lauterbach.com