# Intel® x86/x64 Debugger

Release 02.2025

| TRACE32 Online Help                                |    |

|----------------------------------------------------|----|

| TRACE32 Directory                                  |    |

| TRACE32 Index                                      |    |

| TRACE32 Documents                                  | þ  |

| ICD In-Circuit Debugger                            |    |

| Processor Architecture Manuals                     | þ  |

| x86                                                |    |

| Intel® x86/x64 Debugger                            | 1  |

| History                                            | 7  |

| Brief Overview of Documents for New Users          |    |

| Welcome Dialog                                     | 8  |

| Help Menu                                          | 9  |

| Further Documents                                  | 10 |

| Warning                                            | 12 |

| Quick Start                                        | 13 |

| Troubleshooting                                    | 16 |

| FAQ                                                | 16 |

| x86 specific Implementations                       | 17 |

| Tool Identification                                | 17 |

| Onchip Breakpoints                                 | 17 |

| Breakpoints after Reset/Power Cycle                | 18 |

| Access Classes                                     | 19 |

| Overview                                           | 19 |

| Memory Model                                       | 30 |

| Segmentation                                       | 31 |

| Platform Controller Hub (PCH)                      | 32 |

| Debugging a CPU only                               | 33 |

| Debugging a PCH only                               | 33 |

| Debugging a CPU and a PCH                          | 33 |

| Systems Using a Merged Debug Port                  | 33 |

| Systems Using Separate Debug Ports                 | 34 |

| PCH Selection for CPU Debug on a Merged Debug Port | 34 |

| Slave Core Debugging                               | 34 |

| Start Master Debugger                              | 35 |

| Locating the Slave Core                            | 35 |

|                                                    |    |

Starting the Slave Debugger 36 CPU specific JTAG.CONFIG Commands 37 JTAG.CONFIG Electrical characteristics of MIPI-60 debug signals 37 JTAG.CONFIG.DRiVer Set slew rate of JTAG signals 37 JTAG.CONFIG.PowerDownTriState Automatically tristate outputs 38 JTAG.CONFIG.TckRun Free-running TCK mode 38 38 JTAG.CONFIG.TDOEdge Select TCK edge JTAG.CONFIG.Voltage.HooKTHreshold Set hook threshold voltages 39 JTAG.CONFIG.Voltage.REFerence Set reference voltage source 40 JTAG.CONFIG.Voltage.THreshold Set JTAG threshold voltages 40 CPU specific SYStem.DETECT Commands 41 Show SOC IDs of SOC slave cores 41 SYStem.DETECT.CLTapchain SYStem.DETECT.CORES Detect core/thread number 41 42 SYStem.DETECT.HyperThreads Detect hyper thread status 43 SYStem.DETECT.TARGET Fully automatic board setup SYStem.DETECT.TOPOlogy Detect board topology 44 45 CPU specific SYStem Settings ..... 45 SYStem.CONFIG.state Display target configuration SYStem.CONFIG Configure debugger according to target topology 46 46 Multicore Settings (daisy chain) 49 SYStem.CORESTATES Core states overview Select the target CPU/SOC SYStem.CPU 51 Define JTAG clock SYStem.JtagClock 51 Tristate the JTAG port SYStem.LOCK 51 SYStem.MemAccess 52 Select run-time memory access method SYStem.Mode Establish the communication with the target 52 SYStem.Option.Address32 Use 32 bit address display only 53 54 SYStem.Option.BIGREALmode Enable Big Real mode handling SYStem.Option.BranchSTEP Enables branch stepping 55 SYStem.Option.BreakDELAY Set max. break delay 55 SYStem.Option.C0Hold Hold CPU in C0 state 55 SYStem.Option.IGnoreDEbugReDirections Ignore debug redirections 56 56 SYStem.Option.IGnoreSOC Ignore SoC TAP chain structure SYStem.Option.IGnoreSWBPReDirections Ignore SW BP redirections 56 Disable interrupts while single stepping SYStem.Option.IMASKASM 57 57 SYStem.Option.IMASKHLL Disable interrupts while HLL single stepping SYStem.Option.InstrSUBmitFOrcePHYSicalPRDY Use physical PRDY 57 SYStem.Option.InstrSUBmitIGnorePHYSicalPRDY Ignore physical PRDY 57 SYStem.Option.InstrSUBmitTimeout Timeout for instruction submission 58 SYStem.Option.IntelSOC Slave core is part of Intel® SoC 58 59 SYStem.Option.JTAGDirectCPU JTAG directly to CPU TAPs 59 SYStem.Option.JTAGOnly Use only JTAG signals

| SYStem.Option.MACHINESPACES          |      |

|--------------------------------------|------|

| SYStem.Option.MEMoryMODEL            |      |

| SYStem.Option.MMUSPACES              | Sep  |

| SYStem.Option.MultiCoreWhiskers      |      |

| SYStem.Option.NoDualcoreModule       |      |

| SYStem.Option.NoHyperThread          |      |

| SYStem.Option.NoIPAdjust             |      |

| SYStem.Option.NoReBoot               |      |

| SYStem.Option.OSWakeupTIME           |      |

| SYStem.Option.PC10MODE               |      |

| SYStem.Option.PreserveDRX            |      |

| SYStem.Option.PreserveLBR            |      |

| SYStem.Option.ProbeModeNOSaveResto   | re   |

| SYStem.Option.ProbeModeONDEmand      |      |

| SYStem.Option.PWRCycleTime           |      |

| SYStem.Option.PWROFFTime             |      |

| SYStem.Option.PWRONTime              |      |

| SYStem.Option.PWRONWaitTime          |      |

| SYStem.Option.ReArmBreakPoints       |      |

| SYStem.Option.REL                    |      |

| SYStem.Option.RESetDELAY             |      |

| SYStem.Option.RESetDetection         |      |

| SYStem.Option.RESetMode              |      |

| SYStem.Option.RESetTIME              |      |

| SYStem.Option.RESetWaitTIME          |      |

| SYStem.Option.S0Hold                 |      |

| SYStem.Option.SOFTLONG               | Use  |

| SYStem.Option.STandBYAttach          | In   |

| SYStem.Option.STandBYAttachDELAY     |      |

| SYStem.Option.STepINToEXC            | Ste  |

| SYStem.Option.TOPOlogy               |      |

| SYStem.Option.WatchDogWaitTIME       |      |

| SYStem.Option.WFSMemAccess           |      |

| SYStem.Option.WHISKER                |      |

| SYStem.Option.ZoneSPACES             | En   |

| SYStem.PCH                           |      |

| SYStem.POWER                         |      |

| SYStem.STALLPhase                    |      |

| SYStem.StuffInstruction              | Subn |

| SYStem.StuffInstructionRead          |      |

| SYStem.TIMINGS                       |      |

| Command Groups for Special Registers |      |

CPU specific MMU Commands

| Address extension for guest OSes         | 59 |

|------------------------------------------|----|

| Define memory model                      | 60 |

| Separate address spaces by space IDs     | 63 |

| Server board whisker setup               | 64 |

| Disable dualcore module support          | 64 |

| Disable HyperThreading support           | 65 |

| Do not adjust IP at reset vector         | 65 |

| Disable watchdog causing reboot          | 65 |

| Set the OS wake up time                  | 66 |

| Wake up target from package C10          | 66 |

| Preserve DRx resources                   | 66 |

| Preserve LBR resources                   | 66 |

| No save/restore                          | 67 |

| On demand save/restore                   | 68 |

| Set power cycle time                     | 68 |

| Set power off assertion time             | 68 |

| Set power on assertion time              | 69 |

| Set power on time                        | 69 |

| Rearm breakpoints on reset               | 69 |

| Relocation register                      | 69 |

| Set reset delay                          | 70 |

| Select reset detection source            | 70 |

| Select reset method                      | 71 |

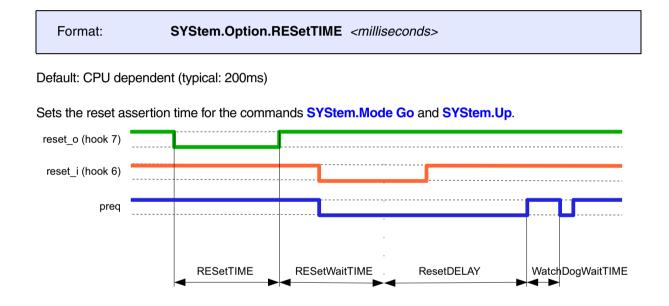

| Set reset assertion time                 | 71 |

| Set reset input wait time                | 71 |

| Hold SoC in S0 state                     | 72 |

| Use 32-bit access to set SW breakpoint   | 72 |

| In standby mode, only attach to target   | 72 |

| Delay after standby                      | 73 |

| Step into interrupt or exception handler | 73 |

| Select server board topology             | 73 |

| Set the reset watch dog time             | 74 |

| Allow WFS memory access                  | 74 |

| Select a whisker                         | 74 |

| Enable symbol management for zones       | 75 |

| Select the target PCH                    | 77 |

| Control target power                     | 77 |

| Set system into stall phase              | 78 |

| Submit instruction to CPU in probe mode  | 78 |

| Submit instruction and read              | 78 |

| Display timings window                   | 79 |

|                                          | 80 |

|                                          |    |

81

| MMU.DUMP                               | Page wise display of MMU translation table | 81  |

|----------------------------------------|--------------------------------------------|-----|

| MMU.List                               | Compact display of MMU translation table   | 85  |

| MMU.SCAN                               | Load MMU table from CPU                    | 87  |

| MMU.Set                                | Set MMU register                           | 88  |

| CPU specific TrOnchip Commands - Oncl  | hip Triggers                               | 89  |

| TrOnchip.PrintList                     | Print possible onchip triggers             | 89  |

| TrOnchip.RESet                         | Reset settings to defaults                 | 89  |

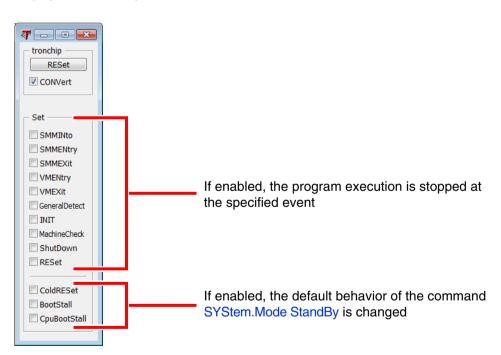

| TrOnchip.Set                           | Break on event                             | 89  |

| TrOnchip.Set.BootStall                 | Enter bootstall                            | 89  |

| TrOnchip.Set.C6Exit                    | Break on C6 exit                           | 91  |

| TrOnchip.Set.ColdRESet                 | Break on cold reset                        | 91  |

| TrOnchip.Set.CpuBootStall              | Enter CPU bootstall                        | 91  |

| TrOnchip.Set.ENCLU                     | Break on ENCLU event                       | 92  |

| TrOnchip.Set.GeneralDetect             | Break on general detect                    | 92  |

| TrOnchip.Set.INIT                      | Break on init                              | 92  |

| TrOnchip.Set.MachineCheck              | Break on machine check                     | 92  |

| TrOnchip.Set.RESet                     | Break on target reset                      | 93  |

| TrOnchip.Set.ShutDown                  | Break on shutdown                          | 93  |

| TrOnchip.Set.SMMENtry                  | Break on SMM entry                         | 93  |

| TrOnchip.Set.SMMEXit                   | Break on SMM exit                          | 93  |

| TrOnchip.Set.SMMINto                   | Step into SMM when single stepping         | 94  |

| TrOnchip.Set.TraceHub                  | Enter/leave trace hub break                | 94  |

| TrOnchip.Set.VMENtry                   | Break on VM entry                          | 94  |

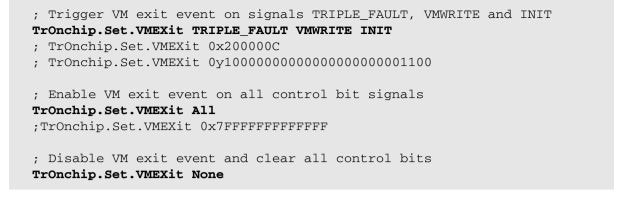

| TrOnchip.Set.VMEXit                    | Break on VM exit                           | 95  |

| TrOnchip.state                         | Display onchip trigger window              | 97  |

| CPU specific Events for the ON and GLO | BALON Command                              | 98  |

| CPU specific BenchmarkCounter Comma    | inds                                       | 99  |

| BMC. <counter></counter>               | Select BMC event to count                  | 99  |

| BMC. <counter>.COUNT</counter>         | Select count mode for BMC                  | 99  |

| CPU specific Onchip Trace Commands     |                                            | 100 |

| Onchip.Buffer                          | Configure onchip trace source              | 100 |

| CPU specific Functions                 |                                            | 102 |

| SYStem.CoreStates.APIC()               |                                            | 102 |

| SYStem.CoreStates.HYPER()              |                                            | 102 |

| SYStem.CoreStates.MODE()               |                                            | 102 |

| SYStem.CoreStates.PHYS()               |                                            | 103 |

| SYStem.CoreStates.PRIOR()              |                                            | 103 |

| SYStem.CoreStates.SMM()                |                                            | 103 |

| SYStem.CoreStates.VMX()                |                                            | 104 |

| SYStem.Option.MEMoryMODEL()            |                                            | 104 |

| SYStem.Option.TOPOlogy()               |                                            | 104 |

| SYStem.Option.TOPOlogy.SOCKETS()       |                                            | 104 |

|   | SYStem.ReadPDRH()                                                      | 105                             |

|---|------------------------------------------------------------------------|---------------------------------|

|   | SYStem.ReadPDRL()                                                      | 105                             |

|   | TrOnchip.IsAvailable()                                                 | 105                             |

|   | TrOnchip.IsSet()                                                       | 106                             |

|   | VMX()                                                                  | 106                             |

|   | VMX.Guest()                                                            | 106                             |

| ç | SYStem Trace Settings                                                  | 107                             |

|   |                                                                        |                                 |

|   | Connectors                                                             | 108                             |

|   | -                                                                      |                                 |

|   | Connectors                                                             | 108                             |

|   | JTAG Connector                                                         | <b>108</b><br>108               |

|   | Connectors<br>JTAG Connector<br>MIPI34 Connector                       | <b>108</b><br>108<br>109        |

|   | Connectors<br>JTAG Connector<br>MIPI34 Connector<br>MIPI60-C Connector | <b>108</b><br>108<br>109<br>110 |

Version 13-Feb-2025

# History

07-Jun-2022 New command: JTAG.CONFIG.TckRun.

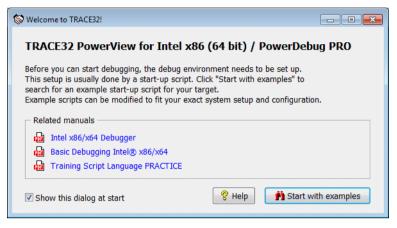

# Welcome Dialog

The **Welcome to TRACE32!** dialog provides access to the most important manuals when TRACE32 is started the first time.

For the Intel<sup>®</sup> x86/x64 architecture the following manuals are listed:

- Intel x86/x64 Debugger is the manual you are currently reading. It provides all the information you need to establish a TRACE32 debug session for an Intel<sup>®</sup> x86/x64 chip.

- **"Training Script Language PRACTICE**" (training\_practice.pdf) teaches you how to write, test and use a start-up script to establish a debug session.

- "Debugger Tutorial" (debugger\_tutorial.pdf) teaches you how to use the standard features of the TRACE32 debugger.

If you unchecked **Show this dialog at start** in the **Welcome to TRACE32!** dialog, you can use the following command to get access to this dialog:

WELCOME.view

The following documents are also good starting points:

"Intel® Application Note for Server Setup" (app\_x86\_server.pdf) explains the configuration of TRACE32 for Intel<sup>®</sup> Xeon<sup>®</sup> server systems.

The following documents are a good starting point for USB Debugging via Intel<sup>®</sup> DCI:

- "Debugging via Intel® DCI User's Guide" (dci\_intel\_user.pdf).

- "Debugging via USB User's Guide" (usbdebug\_user.pdf).

The Help menu provides additionally access to all Training Manuals.

| He          | lp                            |                       |

|-------------|-------------------------------|-----------------------|

| ?           | Contents                      |                       |

| 5           | Index                         |                       |

| 韵           | Find                          |                       |

| <b>1</b> 3: | Tree                          |                       |

| <b>B</b>    | TRACE32 PowerView User Manual |                       |

| <b>B</b>    | Processor Architecture Manual |                       |

| <b>.</b>    | Debugger User Guide           |                       |

| ÷           | Analyzer User Manual          |                       |

|             | Power Probe User Manual       |                       |

| <b>B</b>    | Stimuli Generator User Manual |                       |

| <b>PDF</b>  | Training Manuals              | HLL Debugging         |

| ñ           | Demo Scripts                  |                       |

| \$          | Welcome to TRACE32            | Debugger x86/x64      |

| e           | Setup PDF Viewer              | Intel Processor Trace |

| 6           | Setup PDF Viewer              | 📷 OS Linux x86/x64    |

|             | Lauterbach Homepage           |                       |

|             | Support •                     |                       |

| ۸           | About TRACE32                 |                       |

| -           |                               | -                     |

Beside the Processor Architecture Manual, which is the generic name for this manual within TRACE32 a number of training manuals are provided:

HLL Debugging provides access to "Training Source Level Debugging" (training\_source\_level\_debugging.pdf) which mainly teaches you how to load the application program, how to display and format C-variables.

If you are using C++ refer to "Application Note C++ Debugging" (app\_cpp\_debugging.pdf).

- PRACTICE provides access to "Training Script Language PRACTICE" (training\_practice.pdf).

- Intel Processor Trace provide access to "Training Intel® Processor Tracing" (training\_ipt\_trace.pdf). This manual teaches you how to configure the Intel<sup>®</sup> Processor Trace, how to record trace information, how to analyze and display the recorded information.

All TRACE32 menus can be extended by the user. The following script shows a short example of how to add a manual to the TRACE32 **Help** menu.

```

MENU.ReProgram

(

ADD

MENU

(

POPUP "&Help"

(

AFTER "Processor Architecture Manual"

MENUITEM "[:manual]Intel Processor Trace Manual" "HELP __ICRIPT_"

)

)

)

```

| He         | q                             |

|------------|-------------------------------|

| ?          | <u>C</u> ontents              |

|            | Index                         |

|            | <u>F</u> ind                  |

| 13:        | Tree                          |

| <b>b</b>   | TRACE32 PowerView User Manual |

| pp:        | Processor Architecture Manual |

| <b>.</b>   | Intel Processor Trace Manual  |

| <b>P</b>   | Debugger <u>U</u> ser Guide   |

| ÷          | <u>A</u> nalyzer User Manual  |

|            | Power Probe User Manual       |

| ÷          | Stimuli Generator User Manual |

| <b>PDF</b> | Training Manuals              |

| ñ          | Demo Scripts                  |

| 6          | Welcome to TRACE32            |

| B          | Setup PDF Viewer              |

|            | Lauterbach <u>H</u> omepage   |

|            | Support                       |

| ٨          | About TRACE32                 |

If you need the code of a manual (like \_\_ICRIPT\_ in the above example) please contact support@lauterbach.com.

# **Further Documents**

The following manuals might also be of interest for Intel<sup>®</sup> x86/x64 users:

#### Trace manuals:

• **"Intel® Processor Trace**" (trace\_intel\_pt.pdf) provides configuration information, a command reference for the IPT command group and connector details.

#### UEFI-aware debugging:

- **"UEFI Awareness Manual BLDK**" (uefi\_bldk.pdf) provides configuration information, a feature overview for the TRACE32 UEFI debugger for Intel<sup>®</sup> BLDK, an overview of all relevant EXTension commands and functions.

- **"UEFI Awareness Manual H2O"** (uefi\_h2o.pdf) provides configuration information, a feature overview for the TRACE32 UEFI debugger for InsydeH2O, an overview of all relevant EXTension commands and functions.

#### **OS-aware debugging:**

• **"OS Awareness Manual Linux"** (rtos\_linux\_stop.pdf) provides configuration information, a feature overview for Linux stop-mode debugging, an overview of all relevant commands, functions and error messages.

This manual is automatically added to the TRACE32 Help menu, when the TRACE32 Linux menu is programmed.

This manual is automatically added to the TRACE32 Help menu, when the TRACE32 MSWindows menu is programmed.

The following command allows to add manuals of interest to the Bookmarks tab of the TRACE32 online help:

#### HELP.Bookmark.ADD.file <file> <description> <title>

| 🔑 HELP           |                  |           |                  |           |                |                 |           | 3 |

|------------------|------------------|-----------|------------------|-----------|----------------|-----------------|-----------|---|

| ? Contents       | 🖳 Index          | 疗 Find    | ਸ਼ਿ Command Tree | Bookmarks | 💾 Print        |                 |           |   |

| Selected bookman | rk: 🕞 s          | how dele  | ete              |           |                |                 |           |   |

| Store bookmarks  | to file: 🛛 🗟 Sto | ore 😌 Lo  | ad               |           |                |                 |           |   |

|                  |                  |           |                  |           |                |                 |           |   |

| description      |                  |           | title            |           | filename       |                 |           |   |

| TRACE32 UEFI De  | ebugger for I    | ntel BLDK | UEFI BLDK Debugg | er        | C:\T32_DVD2_20 | 16_Pre\pdf\uefi | _bldk.pdf | * |

|                  |                  |           |                  |           |                |                 |           | Ŧ |

|                  |                  |           |                  |           |                |                 | 4         |   |

| NOTE: |         | ent debugger and target from damage it is recommended to<br>or disconnect the debug cable only while the target power is |

|-------|---------|--------------------------------------------------------------------------------------------------------------------------|

|       | UFF.    |                                                                                                                          |

|       | Recomr  | nendation for the software start:                                                                                        |

|       | 1.      | Disconnect the debug cable from the target while the target power is off.                                                |

|       | 2.      | Connect the host system, the TRACE32 hardware and the debug cable.                                                       |

|       | 3.      | Power ON the TRACE32 hardware.                                                                                           |

|       | 4.      | Start the TRACE32 software to load the debugger firmware.                                                                |

|       | 5.      | Connect the debug cable to the target.                                                                                   |

|       | 6.      | Switch the target power ON.                                                                                              |

|       | 7.      | Configure your debugger e.g. via a start-up script.                                                                      |

|       | Power d | lown:                                                                                                                    |

|       | 1.      | Switch off the target power.                                                                                             |

|       | 2.      | Disconnect the debug cable from the target.                                                                              |

|       | 3.      | Close the TRACE32 software.                                                                                              |

|       | 4.      | Power OFF the TRACE32 hardware.                                                                                          |

After starting TRACE32 PowerView for Intel<sup>®</sup> x86 (64 bit) please proceed as follows to debug your platform:

If you have been provided with a start-up script for your platform, first make sure that the platform is powered. Then simply execute the script as follows:

DO <file>

If you do not have a start-up script and want to debug an Intel<sup>®</sup> Xeon<sup>®</sup> server system platform, please refer to "Intel® Application Note for Server Setup" (app\_x86\_server.pdf) for how to do the necessary setup.

If you do not have a start-up script and want to debug an Intel<sup>®</sup> Atom<sup>TM</sup> or an Intel<sup>®</sup> Core<sup>TM</sup> i3/i5/i7 Client platform, please type (make sure the platform is powered first):

```

SYStem.DETECT TARGET

SYStem.Mode.Attach

Break

```

In most cases this setup is sufficient, and after the commands have been executed successfully it is possible to debug the target, including accessing memory and registers.

If for some reason the above is not successful, please follow the more detailed steps on the next page.

1. First TRACE32 must know which CPU/SOC your platform has. TRACE32 can normally detect this automatically as follows (make sure the platform is powered first):

```

SYStem.DETECT CPU

```

2. Such automatic detection is not supported for all possible platforms. If the automatic detection does not succeed, please select the CPU/SOC of the connected platform directly:

```

SYStem.CPU <cpu> | <soc>

```

3. If you are not sure about the name of the CPU/SOC you can open a window with a list of available names:

SYStem.CPU

Note that this is not a full list of all supported CPUs/SOCs. It only contains names of public, already launched products.

4. Next TRACE32 must know the number of cores/threads of the selected CPU/SOC. This step is required for Intel<sup>®</sup> Core<sup>TM</sup> i3/i5/i7 Client platforms, but can often be skipped for Intel<sup>®</sup> Atom<sup>TM</sup> platforms:

SYStem.DETECT CORES

**NOTE:** SYStem.DETECT TARGET (as used on the previous page) is basically SYStem.DETECT CPU followed by SYStem.DETECT CORES.

5. After the platform CPU/SOC has been detected/selected and the number of cores/threads have been detected (as necessary), further target-specific settings and options can be selected.

But in most cases the default values of other settings and options have automatically been set to the most useful values at this point. This means that in most cases it should now be possible to do basic debugging without any further initial configuration of TRACE32.

6. Attach to the target and enter debug mode.

```

SYStem.Mode.Attach

Break

```

The first command attaches the debugger to the running target. The second command stops the target and enters debug mode (often called *probe mode* for x86/x64 targets). After these commands are executed it is possible to access memory and registers.

A simple start sequence is shown below. This sequence can be written to a PRACTICE script file (\*.cmm, ASCII format) and executed with the command DO < file >.

| RESet                    | ; Reset the TRACE32 software settings       |

|--------------------------|---------------------------------------------|

| WinCLEAR                 | ; Close all windows                         |

| SYStem.DETECT TARGET     | ; Detect platform CPU/SOC and cores/threads |

| SYStem.Mode.Attach       | ; Attach to the running target              |

| Break                    | ; Stop the target and enter debug mode      |

| Register.view /SpotLight | ; Open register and stack window *)         |

| List.Mix                 | ; Open source code window *)                |

\*) These commands open windows on the screen. The window position can be specified with the WinPOS command.

No information available

# FAQ

Please refer to https://support.lauterbach.com/kb.

# **Tool Identification**

The following TRACE32 functions allow you to check which Intel<sup>®</sup> x86/x64 specific TRACE32 tool are controlled by the TRACE32 software.

| hardware.COMBIPROBE()    | Returns TRUE if a TRACE32 CombiProbe is connected.                           |

|--------------------------|------------------------------------------------------------------------------|

| hardware.QUADPROBE()     | Returns TRUE if a TRACE32 QuadProbe is connected.                            |

| ID.WHISKER( <int>)</int> | Returns the identifier for the connected TRACE32 whisker cable.              |

| ID.CABLE()               | Returns 0x3836 if Intel <sup>®</sup> x86/x64 XDP60 Debug Cable is connected. |

```

IF hardware.COMBIPROBE()

(

IF ID.WHISKER(0)==0x10

(

PRINT "Connected Tool is CombiProbe MIPI60-C"

)

IF ID.WHISKER(0)==0x11

(

PRINT "Connected Tool is CombiProbe MIPI60-Cv2"

)

IF ID.WHISKER(0)==(0x2||0x09)

(

PRINT "Connected tool is CombiProbe DCI OOB"

)

)

```

# **Onchip Breakpoints**

The list below gives an overview of the availability and the usage of the **onchip breakpoints**. The following notations are used:

- Onchip breakpoints: Total amount of available onchip breakpoints.

- Instruction breakpoints: Number of onchip breakpoints that can be used to set Program breakpoints.

- Read/Write breakpoints: Number of onchip breakpoints that stop the program when a write or read/write to a certain address happens.

- **Data value breakpoint:** Number of onchip data breakpoints that stop the program when a specific data value is written to an address or when a specific data value is read from an address.

| Family                        | Onchip      | Instruction         | Read/Write                                                                            | Data Value  |

|-------------------------------|-------------|---------------------|---------------------------------------------------------------------------------------|-------------|

|                               | Breakpoints | Breakpoints         | Breakpoint                                                                            | Breakpoints |

| Intel <sup>®</sup><br>x86/x64 | 4           | 4<br>single address | 4<br>Write or<br>Read/Write<br>single address or<br>ranges up to<br>8 bytes (aligned) | _           |

A detailed introduction into the breakpoint handling can be found in "**Breakpoint Handling**" in Training Basic SMP Debugging, page 93 (training\_debugger\_smp.pdf).

# **Breakpoints after Reset/Power Cycle**

TRACE32 PowerView displays **Unknown State** in the **note** column of the **Break.List** window, if TRACE32 detects that the target is reset/re-powered and the cores immediately start the program execution. In this case it is likely that the breakpoint settings are cleared.

| A TRACE32 PowerView for Intel x86/x64                                                |                                                                                      |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| File Edit View Var Break Run CPU Misc Trace Perf Cov I                               | INTELCOUGARPOINT Window Help                                                         |

| ▶ ▶ ▶  ↓ ゼ Ċ   ▶ Ⅱ   巡  ? №  ◎  副 幽 ■                                                | Si Si Si 🅲 🤹 🔑                                                                       |

| 😢 B::Break.List                                                                      |                                                                                      |

|                                                                                      | Store SLoad 🔞 Set                                                                    |

| address types<br>X:000000000400E6C Program<br>X:000000000602E31000000000602E31 Write | imp] note<br>SOFT Unknown State main\6<br>ONCHIP Unknown State vtriplearray[1][1][1] |

| Unknown State                                                                        | h. I                                                                                 |

| B::                                                                                  |                                                                                      |

| B:: <br>trigger devices trace Data Var                                               | List PERF SYStem other previous                                                      |

|                                                                                      | 0 <mark>running HLL UP </mark>                                                       |

## Overview

| Access Class | Description                           |  |

|--------------|---------------------------------------|--|

| С            | Generic                               |  |

| D            | Data                                  |  |

| Р            | Program                               |  |

|              |                                       |  |

| Α            | Absolute                              |  |

| AD           | Absolute Data                         |  |

| АР           | Absolute Program                      |  |

|              |                                       |  |

| I            | Intermediate                          |  |

| ID           | Intermediate Data                     |  |

| IP           | Intermediate Program                  |  |

|              |                                       |  |

| L            | Linear                                |  |

| LD           | Linear Data                           |  |

| LP           | Linear Program                        |  |

|              |                                       |  |

| R            | Real Mode                             |  |

| RD           | Real Mode Data                        |  |

| RP           | Real Mode Program                     |  |

| ARD          | Absolute Real Mode Data               |  |

| ARP          | Absolute Real Mode Program            |  |

| LRD          | Linear Real Mode Data                 |  |

| LRP          | Linear Real Mode Program              |  |

|              |                                       |  |

| N            | Protected Mode (32-bit)               |  |

| ND           | Protected Mode Data (32-bit)          |  |

| NP           | Protected Mode Program (32-bit)       |  |

| AND          | Absolute Protected Mode Data (32-bit) |  |

| Access Class | Description                                           |  |

|--------------|-------------------------------------------------------|--|

| ANP          | Absolute Protected Mode Program (32-bit)              |  |

| LND          | Linear Protected Mode Data (32-bit)                   |  |

| LRP          | Linear Protected Mode Program (32-bit)                |  |

|              |                                                       |  |

| X            | 64-bit Mode                                           |  |

| XD           | 64-bit Mode Data                                      |  |

| ХР           | 64-bit Mode Program                                   |  |

| AXD          | Absolute 64-bit Mode Data                             |  |

| АХР          | Absolute 64-bit Mode Program                          |  |

| LXD          | Linear 64-bit Mode Data                               |  |

| LXP          | Linear 64-bit Mode Program                            |  |

|              |                                                       |  |

| 0            | Protected Mode (16-bit)                               |  |

| OD           | Protected Mode Data (16-bit)                          |  |

| ОР           | Protected Mode Program (16-bit)                       |  |

| AOD          | Absolute Protected Mode Data (16-bit)                 |  |

| AOP          | Absolute Protected Mode Program (16-bit)              |  |

| LOD          | Linear Protected Mode Data (16-bit)                   |  |

| LOP          | Linear Protected Mode Program (16-bit)                |  |

|              |                                                       |  |

| ю            | IO Ports                                              |  |

| MSR          | MSR Registers                                         |  |

| CID          | CPUID Instruction                                     |  |

| VMCS         | VMCS Registers                                        |  |

| IOSF         | IOSF Sideband                                         |  |

|              |                                                       |  |

| Q            | Real Big Mode (Real Mode supporting 32-bit addresses) |  |

| QD           | Real Big Mode Data                                    |  |

| QP           | Real Big Mode Program                                 |  |

| AQD          | Absolute Real Big Mode Data                           |  |

| AQP          | Absolute Real Big Mode Program                        |  |

| Access Class | Description                                               |  |

|--------------|-----------------------------------------------------------|--|

| LQD          | Linear Real Big Mode Data                                 |  |

| LQP          | Linear Real Big Mode Program                              |  |

|              |                                                           |  |

| Е            | Run-time Memory Access                                    |  |

|              |                                                           |  |

| S            | System Management Mode (SMM)                              |  |

| SD           | SMM Data                                                  |  |

| SP           | SMM Program                                               |  |

| SN           | SMM Protected Mode (32-bit)                               |  |

| SND          | SMM Protected Mode Data (32-bit)                          |  |

| SNP          | SMM Protected Mode Program (32-bit)                       |  |

| SX           | SMM 64-bit Mode                                           |  |

| SXD          | SMM 64-bit Mode Data                                      |  |

| SXP          | SMM 64-bit Mode Program                                   |  |

| SO           | SMM Protected Mode (16-bit)                               |  |

| SOD          | SMM Protected Mode Data (16-bit)                          |  |

| SOP          | SMM Protected Mode Program (16-bit)                       |  |

| SQ           | SMM Real Big Mode (Real Mode supporting 32-bit addresses) |  |

| SQD          | SMM Real Big Mode Data                                    |  |

| SQP          | SMM Real Big Mode Program                                 |  |

| AS           | Absolute SMM                                              |  |

| ASD          | Absolute SMM Data                                         |  |

| ASP          | Absolute SMM Program                                      |  |

| LS           | Linear SMM                                                |  |

| LSD          | Linear SMM Data                                           |  |

| LSP          | Linear SMM Program                                        |  |

|              |                                                           |  |

| G            | VMX Guest Mode                                            |  |

| Н            | VMX Host Mode                                             |  |

|              |                                                           |  |

| CSS          | Current value of CS                                       |  |

| Access Class | Description         |  |  |  |

|--------------|---------------------|--|--|--|

| DSS          | Current value of DS |  |  |  |

| SSS          | Current value of SS |  |  |  |

| ESS          | Current value of ES |  |  |  |

| FSS          | Current value of FS |  |  |  |

| GSS          | Current value of GS |  |  |  |

|              |                     |  |  |  |

#### D:, P:

The D: prefix refers to the DS segment register and the P: prefix to the CS segment register. Both D: and P: memory classes access the same memory. It is not possible to split program and data memory. Real Mode or Protected Mode (16, 32 or 64-bit) addressing is chosen dependent on the current processor mode.

| Data.Set P:0x00x0ffff 0x0   | ; fill program memory with zero                 |

|-----------------------------|-------------------------------------------------|

| Data.Set 0x00x0ffff 0x0     | ; fill data memory with zero                    |

| Data.Set 0x100 0x0          | ; set location DS:0x100 to 0                    |

| Data.Assemble 0x100 nop     | ; assemble to location CS:0x100                 |

| Data.Assemble 0x00x0fff nop | ; fill program memory with nop<br>; instruction |

#### A:, AD:, AP:

Absolute addressing. The address parameter specifies the absolute address thus disregarding segmentation and paging. It is possible to use "A" as a prefix to most other memory classes.

| Data.Set A:0x12000 0x33 | ; write to absolute address 0x12000 in<br>; program/data memory |

|-------------------------|-----------------------------------------------------------------|

| Data.dump AD:0x12000    | ; displays absolute address 0x12000<br>; from data memory       |

Intermediate addressing. This memory class is used in connection with virtualization. It corresponds to the guest physical address, i.e., disregards segmentation and paging of the guest, but does not disregard possible second level paging done by the host (use A: for that).

```

Data.Set I:0x12000 0x33 ; write to guest absolute address

; 0x12000 in program/data memory

Data.dump ID:0x12000 ; displays guest absolute address

; 0x12000 from data memory

```

#### L:, LD:, LP:

Linear addressing. The address parameter specifies the linear address thus disregarding segmentation but not paging. It is possible to use "L" as a prefix to most other memory classes.

```

Data.Set L:0x12000 0x33 ; write to linear address 0x12000 in ; program/data memory

Data.dump LD:0x12000 ; displays absolute address 0x12000 ; from data memory

```

#### R:, RD:, RP:

Real Mode addressing.

| Data.Set | R:0x1234:0x5678 | ; | write | to | Real | Mode | address | 0x1234:0x5678 |

|----------|-----------------|---|-------|----|------|------|---------|---------------|

| Data.Set | R:0x100         | ; | write | to | Real | Mode | address | DS:0x100      |

Protected Mode (32-bit) addressing. ("N" is for Normal.)

```

Data.Set N:0x0f0:0x5678; write to Protected Mode address 0x5678 of<br/>; selector 0x0f0Data.dump ND:0x12345678; display memory at Protected Mode address<br/>; DS:0x12345678Data.List NP:0x0C000000; disassemble memory in 32-bit mode at<br/>; Protected Mode address CS:0x0C000000

```

#### X:, XD:, XP:

| 64-bit Mode addressing. ("X" is for eXtended.) |                                                                      |

|------------------------------------------------|----------------------------------------------------------------------|

| Data.dump XD:0x0000123456789ABC                | ;display memory at 64-bit Mode<br>;linear address 0x0000123456789ABC |

#### O:, OD:, OP:

Protected Mode (16-bit) addressing. ("O" is for Old.)

Data.List OP:0x4321

; disassemble memory in 16-bit mode at ; Protected Mode address CS:0x4321

## Q:, QD:, QP:

Big Real Mode addressing. Real Mode (16-bit opcodes), supporting 32-bit addresses. See **SYStem.Option.BIGREALmode ON** for details.

| Data.Set              | ; write to 32-bit Big Real Mode address                  |

|-----------------------|----------------------------------------------------------|

| Q:0x1234:0x5678ABCD   | 0x1234:0x5678ABCD                                        |

| Data.Set Q:0x10008000 | ; write to 32-bit Big Real Mode address<br>DS:0x10008000 |

#### IO:

Access IO ports.

| Data.Out | IO:0xCF8 | %long | 0xF | ; | output | 32-bit | value | 0xF | at | IO | port |

|----------|----------|-------|-----|---|--------|--------|-------|-----|----|----|------|

|          |          |       |     | ; | 0xCF8  |        |       |     |    |    |      |

## MSR:

Accesses MSR registers. The address format is as follows:

| Bits  | Meaning    |

|-------|------------|

| 23-0  | MSR[23-0]  |

| 27-24 | MSR[31-28] |

| 31-28 | Ignored    |

| Data.dump | msr:0x0        | display MSR registers starting with<br>MSR register 0          |

|-----------|----------------|----------------------------------------------------------------|

| Data.dump | msr:0x0C000080 | display MSR registers starting with<br>MSR register 0xC0000080 |

| Bits              | Meaning                                         |

|-------------------|-------------------------------------------------|

| 1-0               | Return Register<br>(0=EAX, 1=EBX, 2=ECX, 3=EDX) |

| 3-2               | Ignored                                         |

| 14-4              | EAX[10-0]                                       |

| 15                | EAX[31]                                         |

| 29-16             | ECX[13-0]                                       |

| 31-30             | Ignored                                         |

|                   |                                                 |

| Data.dump cid:0x0 | ; display CPUID values starting with            |

| Dacardanp |             | ; initial EAX value 0x0                                                                 |

|-----------|-------------|-----------------------------------------------------------------------------------------|

| Data.dump | cid:0x8020  | ; display CPUID values starting with<br>; initial EAX value 0x80000002                  |

| Data.In   | cid:0x20041 | ; return EBX CPUID value with initial<br>; EAX value 0x4 and initial ECX value<br>; 0x2 |

#### VMCS:

Access virtual-machine control data structures (VMCSs). The "address" to be used with this memory class is the corresponding field encoding of an VMCS component.

| , | Data.In | VMCS:0x6C00 | ; display the host CR0 VMCS component |

|---|---------|-------------|---------------------------------------|

|---|---------|-------------|---------------------------------------|

#### IOSF:

Access IOSF sideband.

The address format uses a "<*segment*>:<*offset>*" syntax, where the "segment" is 16 bits, and the "offset" 64 bits:

## IOSF:<8-bit Opcode><8-bit PortID>:<8-bit FID><4-bit BAR><4-bit Reserved><48-bit Address>

"Segment" part:

| Bits | Meaning |

|------|---------|

| 7-0  | Port ID |

| 15-8 | Opcode  |

"Offset" part:

| Bits  | Meaning  |

|-------|----------|

| 47-0  | Address  |

| 51-48 | Reserved |

| 55-52 | BAR      |

| 63-56 | FID      |

| Data.In IOSF:0x0608:3C /long                        | ; Read IOSF sideband with opcode 0x06,<br>; port ID 0x08 and address 0x3C.<br>; (FID and BAR are both 0)    |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Data.Set IOSF:0x0608:3C %long<br>0xdeadbeef         | ; Write IOSF sideband with opcode 0x06,<br>; port ID 0x08 and address 0x3C.<br>; (FID and BAR are both 0)   |

| Data.In<br>IOSF:0x0608:0xFF701234567890A<br>B /long | ; Read IOSF sideband with opcode 0x06,<br>; port ID 0x08, FID 0xFF, BAR 0x7 and<br>; address 0x1234567890AB |

Run-time memory access. This access class must be used for any kind of run-time memory access (be it intrusive or non-intrusive). For that, "E" can be used as a prefix to every other access class.

```

Data.dump END:0x12345678

```

```

; display memory at Protected Mode

; address DS:0x12345678 during run-time

```

#### S:, SD:, SP:, SN:, SND:, SNP:, SX:, SXD:, SXP:, SO:, SOD:, SOP:, SQ:, SQD:, SQP: SR:

The "S" prefix refers to System Management Mode. All these access classes behave like the corresponding ones without the "S" only that they refer to SMM memory instead of normal memory.

```

Data.dump ASD:0x3f300000 ; display SMM memory at absolute

; address 0x3f300000

```

G:, GD:, GP:, GN:, GND:, GNP:, GX:, GXD:, GXP:, GO:, GOD:, GOP:, GQ:, GQD:, GQP: GS:, GSD:, GSP:, GSN:, GSND:, GSNP:, GSX:, GSXD:, GSXP:, GSO:, GSOD:, GSOP:, GSQ:, GSQD:, GSQP: GSR:

When the VMX mode of the target is enabled, TRACE32 indicates the affiliation of logical or linear addresses with the VMX **G**uest mode by adding the prefix "**G**" to the access class.

```

Data.dump GD:0x2a000000 ; display data memory of address

; 0x2a000000 belonging to VMX Guest

; mode

```

H:, HD:, HP:, HN:, HND:, HNP:, HX:, HXD:, HXP:, HO:, HOD:, HOP:, HQ:, HQD:, HQP: HS:, HSD:, HSP:, HSN:, HSND:, HSNP:, HSX:, HSXD:, HSXP:, HSO:, HSOD:, HSOP:, HSQ:, HSQD:, HSQP: HSR:

When the VMX mode of the target is enabled, TRACE32 indicates the affiliation of logical or linear addresses with the VMX Host mode by adding prefix "H" to the access class.

```

Data.dump HD:0x2a000000

```

- ; display data memory of address ; 0x2a000000 belonging to VMX Host

- ; mode

#### Segment register aliases CSS:, DSS:, SSS:, ESS:, FSS:, GSS:

These are not real access classes but aliases which allow to modify the segment descriptor of an address. If one of these six identifiers precedes an address, the value of segment register CS, DS, SS, ES, FS or GS will be used as descriptor in the address.

These aliases are of use only if you want to work directly with segment based addressing in real or protected mode. Note that **SYStem.Option.MEMoryMODEL** must be set to LARGE to support **segmentation** to its fullest extent in protected mode.

**Example**: Let's assume the processor is in protected mode and the segment register FS contains the value 0x18 which is a 32-bit data segment. We want to write to an address with offset 0x12000, using FS as segment register.

| Data.Set  | FSR:0x12000 | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | <pre>write 0x33 to address FSR:0x12000.<br/>Effectively, this will use 0x18 as<br/>segment descriptor.<br/>(If we are in protected mode and FS<br/>is a 32-bit data segment) you could<br/>alternatively use<br/>Data.Set ND:0x18:0x12000 0x33</pre> |

|-----------|-------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data.dump | SSR:0x12000 | ;                                       | display memory at SSR:0x12000                                                                                                                                                                                                                        |

| NOTE: | To avoid confusion with the access classes <b>ES:</b> and <b>GS:</b> , all six segment selector identifiers have been renamed from CS:, DS:, ES:, FS:, GS:, SS: to <b>CSS:</b> , <b>DSS:</b> , <b>ESS:</b> , <b>FSS:</b> , <b>GSS:</b> , <b>SSS:</b> as of TRACE32 build 75425 - DVD 09/2016. |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|       | • Prefix <b>ES:</b> indicates an unspecific (non-program and non-data) dual-port memory accesses in System Management Mode.                                                                                                                                                                   |  |

|       | • Prefix <b>GS:</b> indicates an unspecific system management memory access in VMX Guest Mode.                                                                                                                                                                                                |  |

The Intel® x86 memory model describes the way the debugger considers the six segments CS (code segment), DS (data segment), SS (stack segment), ES, FS and GS and the usage of the LDT (local descriptor table) for the current debug session.

A further introduction into the concept of x86 memory models can be found in the Intel® software developer's manual (please refer to the chapter describing segments in protected mode memory management).

TRACE32 supports a number of memory models when working with addresses and segments: LARGE, FLAT, ProtectedFLAT, LDT and SingleLDT. Activating the space IDs with SYStem.Option.MMUSPACES ON will override any other selected memory model. TRACE32 now behaves as if the memory model FLAT is selected and additionally uses space IDs in the address to identify process-specific address spaces (see SYStem.Option.MMUSPACES for more details).

## Effect of the Memory Model on the Debugger Operation

In protected mode, the address translation of x86 processors support segment translation and paging (if enabled). Segment translation cannot be disabled in hardware. If the TRACE32 address translation is enabled (**TRANSlation.ON**, **TRANSlation.TableWalk ON**), the same translation steps are executed when the debugger performs a memory access to protected mode addresses.

The values loaded into *base, limit* and *attribute* of the segment registers CS, DS, ES, FS, GS and SS depend on the code being executed and how it makes use of the segments. Setup of the segment registers is an essential step in loading executable code into memory. Choosing the appropriate TRACE32 memory model adjusts the segment register handling on the debugger side to the segment register handling on the software side.

For this purpose, TRACE32 offers six memory models. The memory model affects:

- The TRACE32 address format

- Whether or not segment information is used when the debugger accesses memory

- Whether a LDT descriptor is used to dynamically fetch code and data segments from the local descriptor table LDT when the debugger accesses memory

- The way how the segment base and limit values are evaluated when an address is translated from a protected mode address into a linear and/or physical address

- The way the segment attribute information such as code or data width (16/32/64 bit) is evaluated when code or data memory is accessed

For a more detailed description of the memory models supported by TRACE32, see **SYStem.Option.MEMoryMODEL**.

After reset, the TRACE32 memory model **LARGE** is enabled by default. Use one of the following commands to select a different TRACE32 memory model for the current debug session:

- 1. SYStem.Option.MEMoryMODEL

- 2. SYStem.Option.MMUSPACES

- Data.LOAD When loading an executable file, specify one of these command options FLAT, ProtectedFLAT, SingleLDT, LDT, or LARGE to select the TRACE32 memory model you want to apply to the executable.

The PRACTICE function **SYStem.Option.MEMoryMODEL()** returns the name of the currently enabled memory model.

PRINT SYStem.Option.MEMoryMODEL()

;print the name of the memory model ;to the TRACE32 message line

# Segmentation

TRACE32 allows to work with segments, both in real and in protected mode. If the debugger address translation is enabled with **TRANSlation.ON**, real mode or protected mode addresses will be translated to linear addresses. If paging is enabled on the target and the TRACE32 table walk mechanism is enabled with **TRANSlation.TableWalk ON**, the linear addresses will finally be translated to physical addresses.

Segment translation by TRACE32 is only supported if **SYStem.Option.MEMoryMODEL** is set to one of these settings: **LARGE**, **ProtectedFLAT**, **LDT**, **SingleLDT**. For a description of these option, see **SYStem.Option.MEMoryMODEL**. The default option **LARGE**, selected after **SYStem.Up**, is suitable for most debug scenarios where segment translation is used.

Protected mode addresses can be recognized by one of these access classes:

- X:, XD:, XP: (64-bit protected mode)

- N:, ND:, NP: (32-bit protected mode)

- O:, OD:, OP: (16-bit protected mode)

If no segment descriptor is given for such an address, the descriptor from the code segment register (CS) will be augmented to program addresses, and the segment descriptor from the data segment register (DS) will be augmented to data addresses. The command MMU.view can be used to view the current settings of the six segment registers CS, DS, ES, FS, GS, and SS. The augmented segment descriptor is shown as part of the address.

During segment translation of a protected mode address, TRACE32 will extract the segment descriptor from the address and search for it in the six segment registers CS, DS, ES, FS, and GS. If found, the stored values of the segment shadow register (base, limit and attribute) will be used for the linear translation of the protected mode address. Else, a descriptor table walk will be performed through the global descriptor table

GDT, provided the register GDTB (global descriptor table base) points to a valid GDT in memory. If found, the base, limit, and attribute from the GDT entry will be used for the translation. If the address' segment descriptor is not found in the GDT, or the GDT entry is not suitable for the translation of the given address type, the protected mode address cannot be translated to a linear address by TRACE32.

It is possible to explicitly enforce one of the six segment registers CS, DS, ES, FS, GS or SS to be used for the segment translation of an address. This can be accomplished by specifying the segment register instead of a protected mode access class. Use one of the segment register identifiers CSS:, DSS:, ESS:, FSS:, GSS: or SSS: therefore.

**Example**: The address in this **Data.dump** command will use the segment descriptor of segment register FS instead of the default segment descriptor from segment register DS.

Data.dump FSS:0xa7000

NOTE:TRACE32 will not perform segment translation at if the processor is in 64-bit<br/>mode (IA-32e mode). Further, no segment translation is performed for 64-bit<br/>protected mode addresses (addresses with access class X:, XD:, XP:). If no<br/>segment translation is performed, protected mode addresses are translated directly<br/>to linear addresses, disregarding the segment descriptor of the address.This mimics the behavior of the processor, which treats the segment base

registers as zero and performs no segment limit checks if the IA-32e mode (64-bit mode) is enabled.

# Platform Controller Hub (PCH)

All Intel<sup>®</sup> client/server platforms have a Platform Controller Hub (PCH) separate from the CPU. This section describes selection and usage of the PCH in TRACE32. How to select the PCH - and when it is necessary - depends on the usage model and the physical debug port.

There are three types of physical debug ports on Intel<sup>®</sup> client/server platforms:

- 1. Separate CPU debug port (no access to the PCH)

- 2. Separate PCH debug port (no access to the CPU)

- 3. Merged CPU/PCH debug port (access to both CPU and PCH)

Note that most Atom based platforms do not have a separate PCH. For such platforms, most information in this section does not apply.

In the following the three main usage models are described.

When debugging the CPU only, it is normally not required to select a PCH (but see "PCH Selection for CPU Debug on a Merged Debug Port", page 34), and it is advisable to set SYStem.PCH NONE. This is the default setting, so it only needs to be set if it has been changed earlier in the debug session.

```

SYStem.PCH NONE ; there is no PCH

SYStem.CPU <cpu>

SYStem.Option.MultiCoreWhiskers A0 ; select CPU whisker/TCK if needed

```

This setup is applicable to both a separate CPU debug port and a merged CPU/PCH debug port.

## **Debugging a PCH only**

When debugging the PCH only, it is necessary to select NONE for the CPU.

SYStem.PCH <pch> SYStem.CPU NONE ; there is no CPU SYStem.Option.MultiCoreWhiskers D1 ; select PCH whisker/TCK if needed

This setup is applicable to both a separate PCH debug port and a merged CPU/PCH debug port.

### Debugging a CPU and a PCH

#### Systems Using a Merged Debug Port

When debugging a system with the CPU and the PCH on a single merged debug port, it is possible to control both through a single instance of TRACE32. To do so, you must select both the CPU and the PCH:

```

SYStem.PCH <pch>

SYStem.CPU <cpu>

SYStem.Option.MultiCoreWhiskers A0 ; select CPU whisker/TCK if needed

; do not select any PCH whisker/TCK

; TCK1 of the CPU whisker is automatically chosen as PCH whisker

```

Note, with this combined CPU/PCH setup, low-level JTAG shifts can only be made to the CPU from the TRACE32 instance. To make low-level JTAG shifts to the PCH, the merged debug port system must be handled by TRACE32 as having two separate debug ports, see "Systems Using Separate Debug Ports", page 34.

#### Systems Using Separate Debug Ports

When debugging a system with the CPU and the PCH on separate debug ports, you must start two separate instances of TRACE32. The 1st instance must be set up as described in "Debugging a CPU only", page 33, and the 2nd instance must be set up as described in "Debugging a PCH only", page 33. Additionally, the 2nd instance must include the command:

SYStem.CONFIG.Slave off

## PCH Selection for CPU Debug on a Merged Debug Port

There are several cases where it is necessary to select the PCH, even when the main intention is to debug only the CPU on a merged debug port:

- When using a DCI debug port instead of a dedicated Intel XDP60 or Intel MIPI60 debug port. This is because the DCI engine on the target is located in the PCH. For more information on DCI usage, see "Debugging via Intel® DCI User's Guide" (dci\_intel\_user.pdf).

- When the target has a PMODE signal, as PMODE is controlled by the PCH. For more information, see SYStem.Option.RESetDetection.

- When wanting to debug a core in the PCH concurrently with the main CPU. In this case the core

in the PCH must be debugged as a slave in a multicore setup, see "Slave Core Debugging",

page 34.

For all these cases the setup described in "Systems Using a Merged Debug Port", page 33, must be used.

# Slave Core Debugging

Following the steps in the **Quick Start** Section, TRACE32 is set up and attached to an Intel<sup>®</sup> platform. With these steps, you can debug the main application CPU of the platform. All cores of the main CPU are typically handled in a single TRACE32 instance as an SMP setup. Beside the main application CPU cores, there could be other, often special purpose cores, integrated on the same platform. These are called *slave cores* in TRACE32 terminology. On Intel<sup>®</sup> client/server platforms, slave cores can also exist in the PCH. This section describes the steps needed to debug slave cores.

Each slave core requires a dedicated TRACE32 instance in addition to the instance for the main application CPU cores, i.e., an AMP multicore setup is needed. We call the TRACE32 instance that handles the main application CPU cores the *master debugger* and the TRACE32 instance that handles a slave core the *slave debugger*. TRACE32 also supports simultaneous debugging of multiple slave cores using multiple slave debuggers.

A salve cores is first characterized by its core type. Make sure the TRACE32 executable that matches the core type is installed, for example t32mx86 for a 32-bit x86 slave core. Then, if the an SoC integrates multiple slave cores of the same type, TRACE32 needs to know exactly which core your want to debug. This is done by assigning each slave core an SOC ID, which is unique to cores of the same type. If there is just one core of a certain core type, the corresponding ID is always 0.

In general, debugging a slave core consists of 3 steps introduced in the sections below.

## Start Master Debugger

The master debugger must be started before any slave. In the master debugger, follow the **Quick Start** Section to set up the CPU type. If you need to debug a slave core in the PCH, make sure to configure the PCH type as well (see section **Platform Controller Hub**).

The master debugger must be set to at least **Prepare** mode before you can debugging any slave core. If the master debugger remains in **Down** or **NoDebug** mode, the debug port is disabled and no access to the slave core is possible.

## Locating the Slave Core

To find out the ID for a slave core if there is more than one core of that type, use the following command in the **master** debugger.

SYStem.DETECT CLTapchain

A window will open with a column showing the SOC ID associated with each TAP of the platform, including both CPU and PCH. Please consult your Intel<sup>®</sup> support to know if a slave core exists behind a certain TAP and which core type it is.

Note that the SoC ID assignment is valid only for a given CPU and PCH configuration. If you change the CPU or PCH selection in the master debugger, the SOC ID may become different for the same slave core. In this case please re-run this command to get the up-to-date IDs. The following example shows the SOC ID assignment for difference configurations, considering a system that contains 2 x86 slave cores in the CPU and 1 in the PCH.

CPU only

```

SYStem.CPU <cpu_name>

SYStem.PCH NONE

;SOC ID assignment:

;slave core 1 in CPU -> 0

;slave core 2 in CPU -> 1

;slave core in PCH -> N/A

```

#### PCH only

SYStem.CPU NONE

SYStem.PCH <pch\_name>

;SOC ID assignment:

;slave core 1 in CPU -> N/A

;slave core 2 in CPU -> N/A

;slave core in PCH -> 0

#### CPU+PCH

```

SYStem.CPU <cpu_name>

SYStem.PCH <pch_name>

;SOC ID assignment:

;slave core 1 in CPU -> 0

;slave core 2 in CPU -> 1

;slave core in PCH -> 2

```

## Starting the Slave Debugger

In the next step, start the TRACE32 executable that matches the slave core type and do the following setup in the slave debugger:

SYStem.CPU <slave\_core\_type>

SYStem.Option.IntelSOC ON <soc\_id>

;do other slave core specific settings if necessary

SYStem.Mode.Attach

The command **SYStem.Option.IntelSOC** is essential for the slave debugger setup. It indicates TRACE32 to locate the slave core in the master SoC according to its ID, instead of to treat it as a stand-alone core. If there is just one core in the SOC of the chosen core type, the SOC ID argument can be left out.

Note that slave cores in Intel<sup>®</sup> platforms are often protected by security features. A suitable security setting is often needed before such a core can be debugged. Please consult your Intel<sup>®</sup> support to check how to get access to the slave core you are interested in.

# JTAG.CONFIG Electrical characteristics of MIPI-60 debug signals

Using the **JTAG.CONFIG** command group, you can change electrical characteristics of MIPI-60 debug signals to account for target irregularities.

Availability of these commands is dependent on the Debug probe hardware in use.

Many of these commands allow specifying individual whiskers. Multiple whiskers may be selected. Specifying no whiskers indicates that the characteristics of all possible whiskers will be altered.

| JTAG.CONFIG.DRiVer |  |

|--------------------|--|

|--------------------|--|

Set slew rate of JTAG signals

| Format:                    | JTAG.CONFIG.DRiVer. <signal> Fast   Slow [/<whisker>]</whisker></signal> |

|----------------------------|--------------------------------------------------------------------------|

| <i><signal></signal></i> : | all   TCK   TCK0   TCK1   TMS   TDI   nTRST   nPREQ                      |

| <whisker>:</whisker>       | WhiskerA   WhiskerB   WhiskerC   WhiskerD                                |

Default: Fast.

Selects whether to use a series inductor to slow the slew rate of output signals.

| all                                                 | Set rate for all relevant signals.                                         |

|-----------------------------------------------------|----------------------------------------------------------------------------|

| TCK<br>TCK0<br>TCK1<br>TMS<br>TDI<br>nTRST<br>nPREQ | Set rate only for selected signal.                                         |

| FAST                                                | Use direct drive of selected signals.                                      |

| SLOW                                                | Insert inductor on drive of selected signals to limit voltage change rate. |

| Format:              | JTAG.CONFIG.PowerDownTriState ON   OFF [/ <whisker>]</whisker> |

|----------------------|----------------------------------------------------------------|

| <whisker>:</whisker> | WhiskerA   WhiskerB   WhiskerC   WhiskerD                      |

Default: ON.

Enables or disables the automatic setting of all signals to tristate when a power down state of the target is detected.

# JTAG.CONFIG.TckRun

# Free-running TCK mode

[build 143356 - DVD 09/2022]

| Format:              | command.subcommand OFF   TCK0   TCK1 [/ <whisker>]</whisker> |

|----------------------|--------------------------------------------------------------|

| <whisker>:</whisker> | WhiskerA   WhiskerB   WhiskerC   WhiskerD                    |

Default: OFF.

Enables free-running TCK mode for the respective TCK signal.

# JTAG.CONFIG.TDOEdge

### Select TCK edge

| Format:              | JTAG.CONFIG.TDOEdge Rising   Falling [/ <whisker>]</whisker> |

|----------------------|--------------------------------------------------------------|

| <whisker>:</whisker> | WhiskerA   WhiskerB   WhiskerC   WhiskerD                    |

Default: RISING

Selects which edge of TCK signal is used for reading TDO.

| Format:                    | JTAG.CONFIG.Voltage.HooKTHreshold. <signal> <source/> [/<whisker>]<br/>[ON   OFF]</whisker></signal> |

|----------------------------|------------------------------------------------------------------------------------------------------|

| <i><signal></signal></i> : | all   Hook0   Hook6   Hook8   Hook9                                                                  |

| <source/> :                | AUTO<br><voltage></voltage>                                                                          |

| <whisker>:</whisker>       | WhiskerA   WhiskerB   WhiskerC   WhiskerD                                                            |

#### Default: 600mV

Sets voltage threshold to use for determining active state for selected Hook signals.

| all                              | Set threshold for all Hook input signals.          |

|----------------------------------|----------------------------------------------------|

| Hook0<br>Hook6<br>Hook8<br>Hook9 | Set threshold for selected Hook input signal only. |

| Αυτο                             | Use threshold derived from reference voltage.      |

| <voltage></voltage>              | Value in volts to use as threshold.                |

| Format:                                      | JTAG.CONFIG.Voltage.REFerence <source/>            |  |

|----------------------------------------------|----------------------------------------------------|--|

| <source/> :                                  | AUTO<br><voltage></voltage>                        |  |

| Default: AUTO.                               |                                                    |  |

| Selects source to use for reference voltage. |                                                    |  |

| AUTO                                         | Use reference voltage supplied from target system. |  |

*<voltage>* Use specified value in volts as reference voltage.

# JTAG.CONFIG.Voltage.THreshold

Set JTAG threshold voltages

| Format:                    | JTAG.CONFIG.Voltage.THreshold. <signal> <source/> [I<whisker>]</whisker></signal> |

|----------------------------|-----------------------------------------------------------------------------------|

| <i><signal></signal></i> : | all   TDO   PRDY                                                                  |

| <source/> :                | AUTO<br><voltage></voltage>                                                       |

| <whisker>:</whisker>       | WhiskerA   WhiskerB   WhiskerC   WhiskerD                                         |

Default: AUTO.

Sets the voltage threshold to use for determining active state for selected JTAG signals.

| all                 | Set threshold for TDO and PRDY.               |

|---------------------|-----------------------------------------------|

| TDO<br>PRDY         | Set threshold for only selected signal.       |

| Αυτο                | Use threshold derived from reference voltage. |

| <voltage></voltage> | Value in volts to use as threshold.           |

The **SYStem.DETECT** commands detect various configuration parameters of attached target board and apply these parameters to TRACE32.

For information about *architecture-independent* **SYStem.DETECT** commands, refer to "General Commands Reference Guide S" (general\_ref\_s.pdf).

For information about *architecture-specific* **SYStem.DETECT** commands, see command descriptions below.

| SYStem.DETECT.C | CLTapchain |

|-----------------|------------|

|-----------------|------------|

# Show SOC IDs of SOC slave cores

Format:

SYStem.DETECT.CLTapchain

See "Locating the Slave Core", page 35.

# SYStem.DETECT.CORES

Detect core/thread number

Format:

SYStem.DETECT.CORES

The command **SYStem.DETECT.CORES** detects the core number and the hyper thread status of the target board. The setup of TRACE32 is changed accordingly.

This command requires:

- Topology configuration (with SYStem.Option.TOPOlogy)

- Whisker configuration (with SYStem.Option.MultiCoreWhiskers)

- CPU configuration (with SYStem.DETECT.CPU or SYStem.CPU)

Format: SYStem.DETECT.HyperThreads

The command **SYStem.DETECT.HyperThreads** detects the hyper thread status of the CPU. The setup of TRACE32 is changed accordingly. This command is intended for analysis and not for target board setup.

This command requires:

- Topology configuration (with SYStem.Option.TOPOlogy)

- Whisker configuration (with SYStem.Option.MultiCoreWhiskers)

- CPU configuration (with SYStem.DETECT.CPU or SYStem.CPU)

| Format: | SYStem.DETECT.TARGET | [/ <option>] [/Verbose]</option> |

|---------|----------------------|----------------------------------|

|---------|----------------------|----------------------------------|

<option>: Auto | CPUonly | PCHonly

The command SYStem.DETECT.TARGET detects all required board setup parameters:

- The board topology

- The required whiskers for the detected topology