# QorlQ Debugger and NEXUS Trace

Release 09.2024

| TRACE32 Online Help                                               |    |

|-------------------------------------------------------------------|----|

| TRACE32 Directory                                                 |    |

| TRACE32 Index                                                     |    |

| TRACE32 Documents                                                 |    |

| ICD In-Circuit Debugger                                           | Þ  |

| Processor Architecture Manuals                                    |    |

| QorlQ                                                             |    |

| QorIQ Debugger and NEXUS Trace                                    | 1  |

| Introduction                                                      | 6  |

| Brief Overview of Documents for New Users                         | 6  |

| Demo and Start-up Scripts                                         | 7  |

| Warning                                                           | 8  |

| Target Design Recommendations                                     | 9  |

| General                                                           | 9  |

| Quick Start                                                       | 10 |

| Troubleshooting                                                   | 11 |

| SYStem.Up Errors                                                  | 11 |

| FAQ                                                               | 12 |

| Tool Configuration                                                | 13 |

| TRACE32 Debugger                                                  | 13 |

| TRACE32 Debugger and Trace with Serial Preprocessor               | 14 |

| TRACE32 Debugger and Trace with PowerTrace Serial                 | 16 |

| Aurora Traceport                                                  | 16 |

| PCIe Traceport                                                    | 19 |

| PowerPC QorlQ specific Implementations                            | 20 |

| Breakpoints                                                       | 20 |

| Software Breakpoints                                              | 20 |

| On-chip Breakpoints                                               | 20 |

| Breakpoints on Program Addresses                                  | 21 |

| Breakpoints on Data Addresses                                     | 22 |

| Breakpoints on Data Access at Program Address                     | 22 |

| Breakpoints on Data Value                                         | 23 |

| Access Classes                                                    | 24 |

| Access Classes to Memory and Memory Mapped Resources              | 24 |

| Access Classes to Other Addressable Core and Peripheral Resources | 25 |

| Cache                             |                                                 | 26 |

|-----------------------------------|-------------------------------------------------|----|

| Memory Coherency                  |                                                 | 26 |

| MESI States and Cache Status Flag | js                                              | 27 |

| Viewing Cache Contents            |                                                 | 28 |

| Debugging Information             |                                                 | 29 |

| Multicore Debugging               |                                                 | 29 |

| General Information               |                                                 | 29 |

| SMP Debugging                     |                                                 | 30 |

| AMP Debugging                     |                                                 | 31 |

| Synchronous Go of the Cores       |                                                 | 34 |

| Synchronous Stop of the Cores     |                                                 | 34 |

| Programming Flash on QorlQ Proce  | essors                                          | 38 |

| Programming the Reset Configurati | on Word (RCW)                                   | 39 |

| Trace Information                 |                                                 | 40 |

| Supported Trace Features          |                                                 | 41 |

| Aurora HSTP Trace                 |                                                 | 42 |

| Nexus PCIe Trace                  |                                                 | 42 |

| On-chip Trace                     |                                                 | 44 |

| Trace initialization              |                                                 | 45 |

| Trace Sink settings and processe  | s - depending on the system state               | 45 |

| Trace Source settings and trace a | access - regardless of the system state         | 46 |

| CPU specific SYStem Commands      |                                                 | 48 |

| SYStem.BdmClock                   | Set debug clock frequency                       | 48 |

| SYStem.CONFIG.state               | Display target configuration                    | 49 |

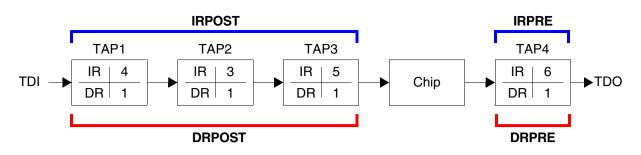

| SYStem.CONFIG                     | Configure debugger according to target topology | 50 |

| SYStem.CONFIG.CHKSTPIN            | Control pin 8 of debug connector                | 53 |

| SYStem.CONFIG.DriverStrength      | Configure driver strength of TCK pin            | 54 |

| SYStem.CONFIG.QACK                | Control QACK pin                                | 54 |

| SYStem.CPU                        | Select the CPU type                             | 55 |

| SYStem.LOCK                       | Lock and tristate the debug port                | 55 |

| SYStem.MemAccess                  | Select run-time memory access method            | 55 |

| SYStem.Mode                       | Select operation mode                           | 57 |

| CPU specific SYStem.Option Comma  | ands                                            | 58 |

| SYStem.Option.Address32           | Define address format display                   | 58 |

| SYStem.Option.DCFREEZE            | Data cache state frozen while core halted       | 58 |

| SYStem.Option.DCREAD              | Read from data cache                            | 59 |

| SYStem.Option.DUALPORT            | Implicitly use run-time memory access           | 60 |

| SYStem.Option.FREEZE              | Freeze system timers on debug events            | 60 |

| SYStem.Option.HOOK                | Compare PC to hook address                      | 60 |

| SYStem.Option.HRCWOVerRide        | Override RCW during SYStem.Up                   | 61 |

| SYStem.Option.ICFLUSH             | Invalidate instruction cache before go and step | 61 |

| SYStem.Option.ICREAD              | Read from instruction cache                     | 61 |

| SYStem.Option.IMASKASM            | Disable interrupts while single stepping        | 62 |

|                                   |                                                 |    |

| SYStem.Option.IMASKHLL<br>SYStem.Option.MACHINESPACES<br>SYStem.Option.MMUSPACES<br>SYStem.Option.NoDebugStop<br>SYStem.Option.OVERLAY<br>SYStem.Option.RESetBehavior<br>SYStem.Option.SLOWRESET<br>SYStem.Option.STEPSOFT<br>SYStem.Option.TranslationSPACE<br>SYStem.Option.ZoneSPACES | Disable interrupts while HLL single stepping<br>Address extension for guest OSes<br>Separate address spaces by space IDs<br>Disable JTAG stop on debug events<br>Enable overlay support<br>Set behavior when target reset detected<br>Relaxed reset timing<br>Use alternative method for ASM single step<br>Identify user and hypervisor modes<br>Enable symbol management for zones | 62<br>63<br>65<br>66<br>67<br>67<br>68<br>68<br>68 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| CPU specific MMU Commands                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                      | 73                                                 |

| MMU.DUMP                                                                                                                                                                                                                                                                                 | Page wise display of MMU translation table                                                                                                                                                                                                                                                                                                                                           | 73                                                 |

| MMU.FORMAT                                                                                                                                                                                                                                                                               | Define MMU table structure                                                                                                                                                                                                                                                                                                                                                           | 76                                                 |

| MMU.List                                                                                                                                                                                                                                                                                 | Compact display of MMU translation table                                                                                                                                                                                                                                                                                                                                             | 82                                                 |

| MMU.SCAN                                                                                                                                                                                                                                                                                 | Load MMU table from CPU                                                                                                                                                                                                                                                                                                                                                              | 84                                                 |

| MMU.Set                                                                                                                                                                                                                                                                                  | Set an MMU TLB entry                                                                                                                                                                                                                                                                                                                                                                 | 86                                                 |

| CPU specific BenchMarkCounter Commar                                                                                                                                                                                                                                                     | nds                                                                                                                                                                                                                                                                                                                                                                                  | 87                                                 |

| BMC.FREEZE                                                                                                                                                                                                                                                                               | Freeze counters while core halted                                                                                                                                                                                                                                                                                                                                                    | 87                                                 |

| BMC.Trace                                                                                                                                                                                                                                                                                | Trace performance monitor events                                                                                                                                                                                                                                                                                                                                                     | 87                                                 |

| BMC. <counter>.FREEZE</counter>                                                                                                                                                                                                                                                          | Freeze counter in certain core states                                                                                                                                                                                                                                                                                                                                                | 88                                                 |

| CPU specific TrOnchip Commands                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                      | 89                                                 |

| TrOnchip.CONVert                                                                                                                                                                                                                                                                         | Adjust range breakpoint in on-chip resource                                                                                                                                                                                                                                                                                                                                          | 89                                                 |

| TrOnchip.RESet                                                                                                                                                                                                                                                                           | Reset on-chip trigger settings                                                                                                                                                                                                                                                                                                                                                       | 90                                                 |

| TrOnchip.Set                                                                                                                                                                                                                                                                             | Enable special on-chip breakpoints                                                                                                                                                                                                                                                                                                                                                   | 90                                                 |

| TrOnchip.VarCONVert                                                                                                                                                                                                                                                                      | Adjust HLL breakpoint in on-chip resource                                                                                                                                                                                                                                                                                                                                            | 91                                                 |

| TrOnchip.state                                                                                                                                                                                                                                                                           | View on-chip trigger setup window                                                                                                                                                                                                                                                                                                                                                    | 92                                                 |

| Nexus and Trace specific commands                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                      | 93                                                 |

| DDRTrace.List                                                                                                                                                                                                                                                                            | List DDR trace contents                                                                                                                                                                                                                                                                                                                                                              | 93                                                 |

| DQMTrace.List                                                                                                                                                                                                                                                                            | List DQM trace contents                                                                                                                                                                                                                                                                                                                                                              | 93                                                 |

| NEXUS.BTM                                                                                                                                                                                                                                                                                | Enable program trace messaging                                                                                                                                                                                                                                                                                                                                                       | 94                                                 |

| NEXUS.CoreENable                                                                                                                                                                                                                                                                         | Core specific trace configuration                                                                                                                                                                                                                                                                                                                                                    | 94                                                 |

| NEXUS.DDRConfig.ADDRessfilter                                                                                                                                                                                                                                                            | Filter Nexus DDR messages                                                                                                                                                                                                                                                                                                                                                            | 95                                                 |

| NEXUS.DDRConfig.Controller                                                                                                                                                                                                                                                               | Configure Nexus DDR message type                                                                                                                                                                                                                                                                                                                                                     | 95                                                 |

| NEXUS.DQM                                                                                                                                                                                                                                                                                | Enable data acquisition messaging                                                                                                                                                                                                                                                                                                                                                    | 96                                                 |

| NEXUS.LaneMapping                                                                                                                                                                                                                                                                        | Logical to physical lane mapping                                                                                                                                                                                                                                                                                                                                                     | 97                                                 |

| NEXUS.LaneMapping.APPLY                                                                                                                                                                                                                                                                  | Apply logical to physical lane mapping                                                                                                                                                                                                                                                                                                                                               | 97                                                 |

| NEXUS.LaneMapping.SetLane                                                                                                                                                                                                                                                                | Configure logical to physical lane mapping                                                                                                                                                                                                                                                                                                                                           | 97                                                 |

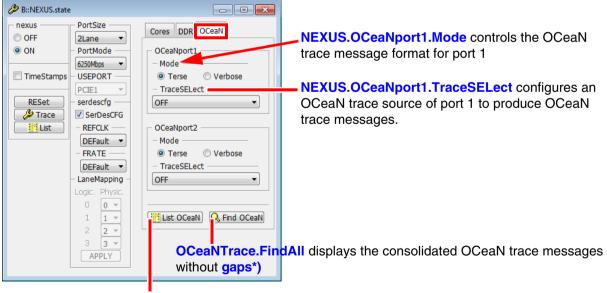

| NEXUS.OCeaNport.Mode                                                                                                                                                                                                                                                                     | Configure Nexus OCeaN message type                                                                                                                                                                                                                                                                                                                                                   | 98                                                 |

| NEXUS.OCeaNport <index>.TraceSELect</index>                                                                                                                                                                                                                                              | Select Nexus OCeaN trace type                                                                                                                                                                                                                                                                                                                                                        | 99                                                 |

| NEXUS.OFF                                                                                                                                                                                                                                                                                | Switch the Nexus trace port off                                                                                                                                                                                                                                                                                                                                                      | 99                                                 |

| NEXUS.ON                                                                                                                                                                                                                                                                                 | Switch the Nexus trace port on                                                                                                                                                                                                                                                                                                                                                       | 100                                                |

| NEXUS.OTM                                                                                                                                                                                                                                                                                | Enable ownership trace messaging                                                                                                                                                                                                                                                                                                                                                     | 100                                                |

|                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                      |                                                    |

| NEXUS.PortMode                         | Set Nexus trace port frequency                         | 101 |

|----------------------------------------|--------------------------------------------------------|-----|

| NEXUS.PortSize                         | Set trace port width                                   | 101 |

| NEXUS.POTD                             | Disable periodic ownership trace                       | 102 |

| NEXUS.PTCM                             | Enable program trace correlation messages              | 102 |

| NEXUS.PTFGS                            | Program trace mark                                     | 102 |

| NEXUS.PTFPMM                           | Program trace mark                                     | 103 |

| NEXUS.PTFPR                            | Program trace mark                                     | 103 |

| NEXUS.PTMARK                           | Program trace mark                                     | 104 |

| NEXUS.RefClock                         | Enable Aurora reference clock                          | 104 |

| NEXUS.Register                         | Display NEXUS trace control registers                  | 104 |

| NEXUS.RESet                            | Reset Nexus trace port settings                        | 105 |

| NEXUS.SerDesCFG                        | Enable SerDes PLL control register manipulation        | 105 |

| NEXUS.SerDesCFG.FRATE                  | Select frequency of SerDes PLL VCO                     | 105 |

| NEXUS.SerDesCFG.REFCLK                 | Select frequency of SerDes reference clock             | 106 |

| NEXUS.Spen <messagetype></messagetype> | Enable message suppression                             | 106 |

| NEXUS.STALL                            | Stall the program execution when FIFO level is reached | 107 |

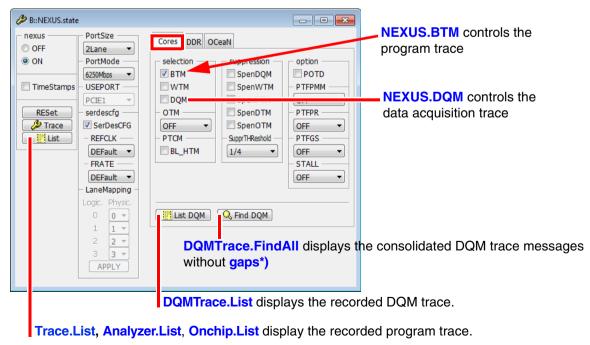

| NEXUS.state                            | Display Nexus port configuration window                | 108 |

| NEXUS.SupprTHReshold                   | Set fill level for message suppression                 | 108 |

| NEXUS.TimeStamps                       | Append target timestamps to Nexus messages             | 109 |

| NEXUS.USEPORT                          | Define used PCIe controller for PCIe trace             | 109 |

| NEXUS.WTM                              | Enable watchpoint messaging                            | 109 |

| OCeaNTrace.List                        | List OCeaN trace contents                              | 110 |

| Onchip specific Commands               |                                                        | 111 |

| Onchip.TBARange                        | Configure on-chip trace base address range             | 111 |

| Filters and Triggers for the Nex       | us Trace                                               | 112 |

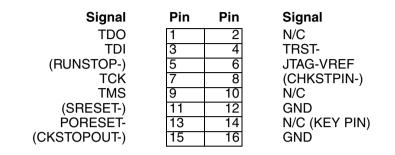

| JTAG Connector                         |                                                        | 114 |

| Mechanical Description                 |                                                        | 114 |

| JTAG Connector QorlQ (COF              | 2)                                                     | 114 |

| Aurora HSTP Connectors                 |                                                        | 115 |

| Samtec22 (Power.org)                   |                                                        | 115 |

| Samtec46 (Power.org)                   |                                                        | 115 |

| Samtec70 (Power.org)                   |                                                        | 116 |

|                                        |                                                        |     |

Version 05-Oct-2024

# Introduction

This document describes the processor specific settings and features for TRACE32-ICD for the following CPU families:

- QorIQ Series with e500mc cores (P204X, P30XX, P40XX)

- QorlQ Series with e5500 cores (P50XX, T10XX)

- QorIQ Series with e6500 cores (T2XXX, T4XXX, B4XXX)

Please keep in mind that only the **Processor Architecture Manual** (the document you are reading at the moment) is CPU specific, while all other parts of the online help are generic for all CPUs supported by Lauterbach. So if there are questions related to the CPU, the Processor Architecture Manual should be your first choice.

If some of the described functions, options, signals or connections in this Processor Architecture Manual are only valid for a single CPU or for specific families, the name(s) of the family(ies) is added in brackets.

# **Brief Overview of Documents for New Users**

#### Architecture-independent information:

- **"Training Basic Debugging"** (training\_debugger.pdf): Get familiar with the basic features of a TRACE32 debugger.

- **"T32Start**" (app\_t32start.pdf): T32Start assists you in starting TRACE32 PowerView instances for different configurations of the debugger. T32Start is only available for Windows.

- **"General Commands**" (general\_ref\_*<x>*.pdf): Alphabetic list of debug commands.

#### Architecture-specific information:

- "Processor Architecture Manuals": These manuals describe commands that are specific for the processor architecture supported by your Debug Cable. To access the manual for your processor architecture, proceed as follows:

- Choose Help menu > Processor Architecture Manual.

- "OS Awareness Manuals" (rtos\_<os>.pdf): TRACE32 PowerView can be extended for operating system-aware debugging. The appropriate OS Awareness manual informs you how to enable the OS-aware debugging.

Lauterbach provides ready-to-run start-up scripts for known QorIQ based hardware.

#### To search for PRACTICE scripts, do one of the following in TRACE32 PowerView:

- Type at the command line: WELCOME.SCRIPTS

- or choose File menu > Search for Script.

You can now search the demo folder and its subdirectories for PRACTICE start-up scripts (\*.cmm) and other demo software.

You can also manually navigate in the ~~/demo/powerpc64bit/ subfolder of the system directory of TRACE32.

# Warning

# Signal Level

| P204X<br>P30XX<br>P40XX<br>P50XX<br>T10XX<br>T2XXX<br>T4XXX<br>B4XXX | The debugger drives the output pins of the BDM/JTAG/COP connector with the same level as detected on the VCCS pin. If the IO pins of the processor are 3.3 V compatible then the VCCS should be connected to 3.3 V. See also <b>System.up Errors</b> . |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

## **ESD** Protection

| r        |                                                                                                                                           |                                                                           |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|

| WARNING: | To prevent debugger and target from damage it is recommended to connect or disconnect the Debug Cable only while the target power is OFF. |                                                                           |  |

|          | Recom                                                                                                                                     | mendation for the software start:                                         |  |

|          | 1.                                                                                                                                        | Disconnect the Debug Cable from the target while the target power is off. |  |

|          | 2.                                                                                                                                        | Connect the host system, the TRACE32 hardware and the Debug Cable.        |  |

|          | 3.                                                                                                                                        | Power ON the TRACE32 hardware.                                            |  |

|          | 4.                                                                                                                                        | Start the TRACE32 software to load the debugger firmware.                 |  |

|          | 5.                                                                                                                                        | Connect the Debug Cable to the target.                                    |  |

|          | 6.                                                                                                                                        | Switch the target power ON.                                               |  |

|          | 7.                                                                                                                                        | Configure your debugger e.g. via a start-up script.                       |  |

|          | Power c                                                                                                                                   | lown:                                                                     |  |

|          | 1.                                                                                                                                        | Switch off the target power.                                              |  |

|          | 2.                                                                                                                                        | Disconnect the Debug Cable from the target.                               |  |

|          | 3.                                                                                                                                        | Close the TRACE32 software.                                               |  |

|          | 4.                                                                                                                                        | Power OFF the TRACE32 hardware.                                           |  |

## General

- Locate JTAG/COP and Aurora NEXUS connectors as close as possible to the processor to minimize the capacitive influence of the trace length and cross coupling of noise onto the JTAG signals. Do not put any termination (e.g. R/C/RC) on the JTAG lines.

- Connect TDI, TDO, TMS and TCK directly to the CPU. Buffers on the JTAG lines will add delays and will reduce the maximum possible JTAG frequency. If you need to use buffers, select ones with little delay. Most CPUs will support JTAG above 20 MHz, and you might want to use high frequencies for optimized download performance.

- For optimal operation, the debugger should be able to reset the target board completely (processor external peripherals, e.g. memory controllers) with the COP connector signal HRESET (respectively the CPU pin PORESET). For further details please see the QorlQ documents "Integrated Processor Hardware Specifications", part "Hardware design considerations".

- In order to start debugging right from reset, the debugger must be able to control the COP connector signals TRST and HRESET independent of each other.

# **Quick Start**

Starting up the Debugger is done as follows:

1. Select the device prompt B: for the ICD Debugger, if the device prompt is not active after the TRACE32 software was started.

B::

2. Select the CPU type to load the CPU specific settings. If your CPU is not listed, you should request a software update that handles this CPU.

SYStem.CPU P4080

3. Specify that on-chip breakpoints should be used by the debugger if a program breakpoint is set to the boot page (read-only memory):

**MAP.BOnchip** 0xFFFFF000--0xFFFFFFF

4. Enter active debug mode.

SYStem.Up

This command resets the CPU (HRESET), enters debug mode and stops all cores of the CPU at the reset vector. See also **SYStem.Up Errors** if problems occur.

5. After **SYStem.Up**, only the boot page is visible for the CPU. Specify Local Access Windows (LAWs) and initialize MMU TLBs to configure which memory is visible to the CPU at which address. In the example, we map the P4080 internal SRAM (CoreNet platform cache) to logical address 0x00000000. See MMU.Set.TLB and Data.Set for details.

Data.Set

ANC:iobase.address()+0x0C00

%LONG

%BE

0x00000000

;Set

Data.Set

ANC:iobase.address()+0x0C04

%LONG

%BE

0x00000000

;LAW

0

Data.Set

ANC:iobase.address()+0x0C08

%LONG

%BE

0x81000013

;and

MMU.Set.TLB1

1.

0x80000500

0x0000002

0x00000015

0x00000000

;TLB

1

6. Load the program.

Data.LOAD.ELf demo.elf

;(ELF specifies the format, ;demo.elf is the file name)

The option of the **Data.LOAD** command depends on the file format generated by the compiler. A detailed description of the **Data.LOAD** command is given in the "General Commands Reference".

# SYStem.Up Errors

The **SYStem.Up** command is the first command of a debug session where communication with the target is required. If you receive error messages while executing this command, there can be several reasons. The following chapters list possible errors and explain how to fix them.

#### **Target Power Fail**

The Target has no power, the debug cable is not connected or not connected properly. Check if the JTAG VCC pin is driven by the target. The voltage of the pin must be identical to the debug voltage of the JTAG signals. It is recommended to connect VCC directly to the pin, or via a resistor < 5 kOhm.

## **Debugger Configuration Error**

The debugger was not able to determine the connected processor. There are three possible reasons for this error. In all cases, please check the **AREA** window for more information:

- The connected processor is not supported by the used software. Please check if the processor is supported by the debugger. Processors that appeared later than the debugger software version are usually not supported. Please download and install the latest software from our website, or contact technical support to get a newer software. Please also check if the processor or the software update is covered by your current licence.

- A JTAG communication error prevented correct determination of the connected processor. Please check if the debugger is properly connected to the target.

## **Target Reset Fail**

On **SYStem.Up**, the debugger will assert **HRESET** in order to stop the CPU at the reset address. A target reset fail means, that an unexpected reset behavior caused an error:

- The reset is asserted longer than 500ms and is not visible on the JTAG connector. Try **SYStem.Option.SLOWRESET**, and check signal level of the JTAG HRESET pin.

- The target reset is permanently asserted. Check target reset circuitry and reset pull-up.

- A chip external watchdog caused a reset after the debugger asserted reset. Disable the watchdog and try again.

An emulation debug port fail can have a variety of reasons. Please check the **AREA** window for a detailed error message. Here is a collection of frequent issues:

- JTAG communication error. Please check the signals on the debug connector.

- Problems related with Reset can not always be detected as those. Please check Target Reset Fail.

#### CPU Setting Error

• The detected quantity of cores does not fit to the CPUs default. Most QorIQ CPUs offer the possibility to completely disable cores (typically via the dedicated TEST\_SEL pin). If any of the cores are disabled you have to configure the debugger to restrict the access to the active cores using the **CORE.ASSIGN** command.

```

; e.g. P2041, TEST_SEL wired to high level.

; -> Just the first two cores are active.

SYStem.CPU P2041

SYStem.Up ;Expected 4 active cores -> Error message

CORE.ASSIGN 1,2 ;Configure the active usable cores

SYStem.Up ;Debugging possible

```

# FAQ

Please refer to https://support.lauterbach.com/kb.

QorIQ development boards typically offer one of the following connector options:

- JTAG connector only

- JTAG connector and Aurora connector (Power.org 22-, 46- or 70-pin connector)

- Aurora connector only (Power.org 22-, 46- or 70-pin connector)

Depending on your board, you might need to adjust some board specific settings to define which connector you want to use. Please refer to the configuration sheet of your board for further details.

If you want to start debugging right away, then simply check the two configuration options and use the working one. For the working configuration option, TRACE32 accepts the **SYStem.Up** command without displaying an error message.

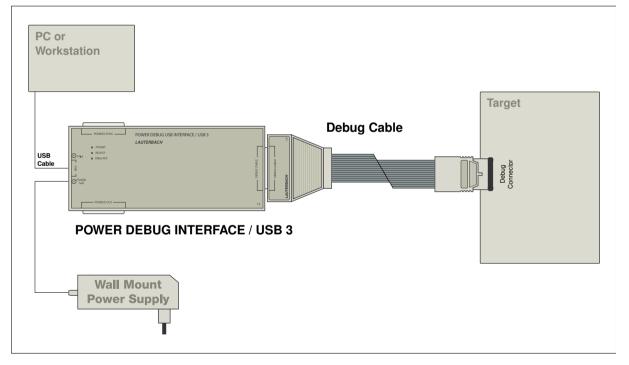

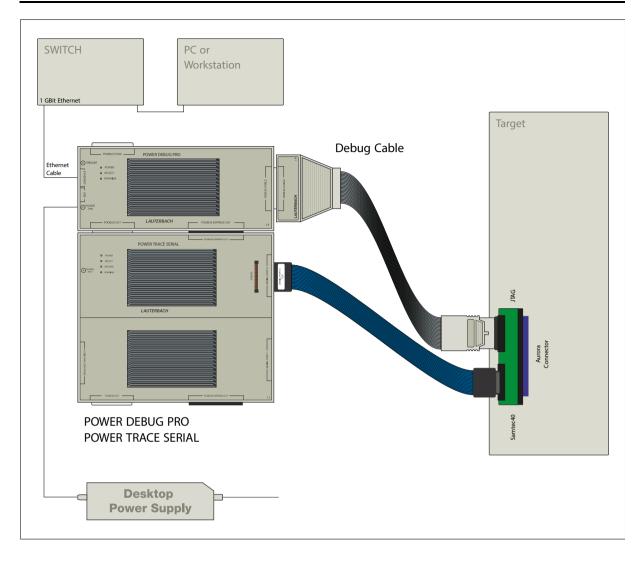

# **TRACE32** Debugger

A QorIQ development board that allows only debugging, typically comes with a JTAG connector.

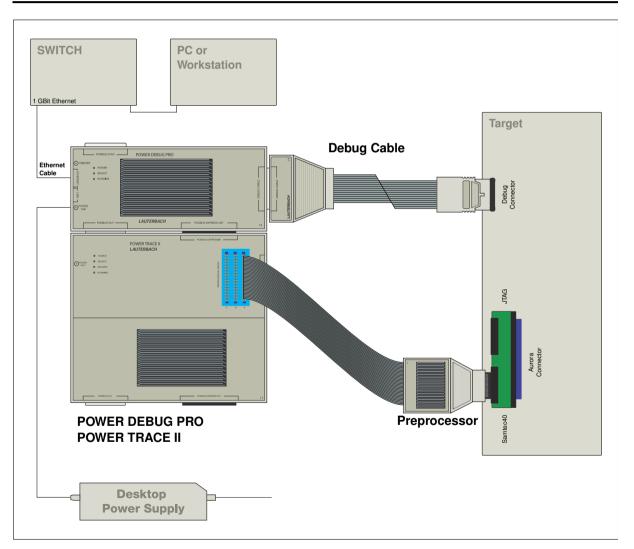

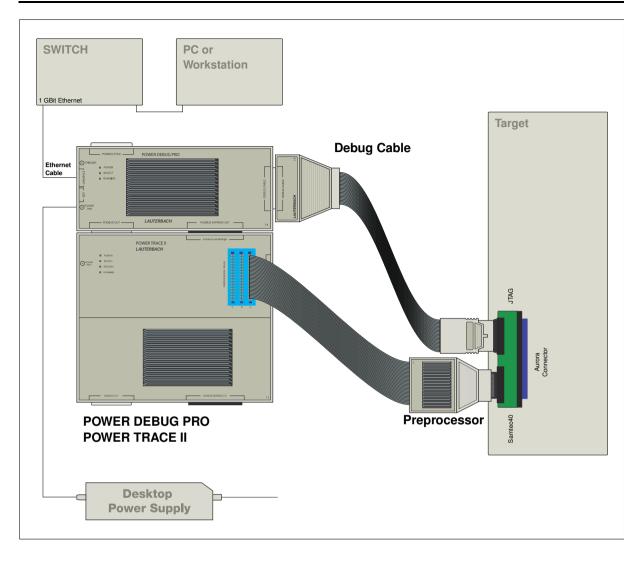

The TRACE32 PREPROCESSOR SERIAL for the QorIQ has a 40-pin connector. If you are using a Power.org defined connector (22-, 46- or 70-pin) on your target you will need a fitting Aurora converter to connect TRACE32 PREPROCESSOR SERIAL.

All Lauterbach Aurora converters provide a JTAG connector and a Samtec40 connector for the tool side and a Power.org connector for the target side. Depending on your board design you have to use either:

- The board JTAG connector to connect the TRACE32 Debug Cable and the Lauterbach Aurora converter to connect the TRACE32 Serial Preprocessor.

- Or you use the Aurora converter to connect both, the TRACE32 Debug Cable and the TRACE32 Serial Preprocessor.

#### JTAG and Aurora Connector

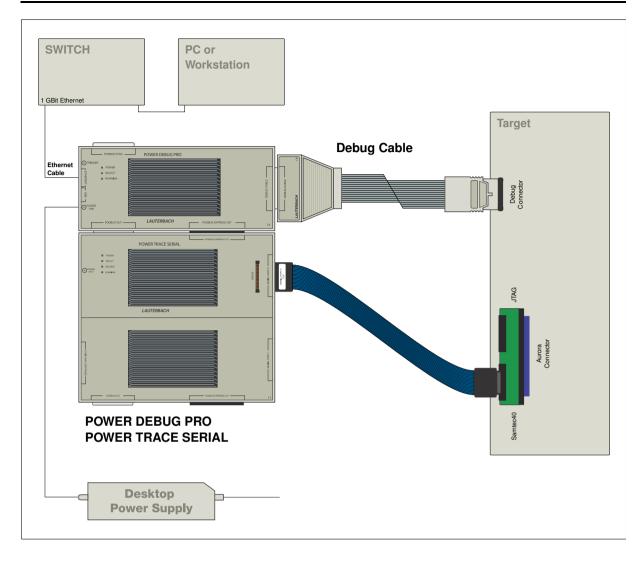

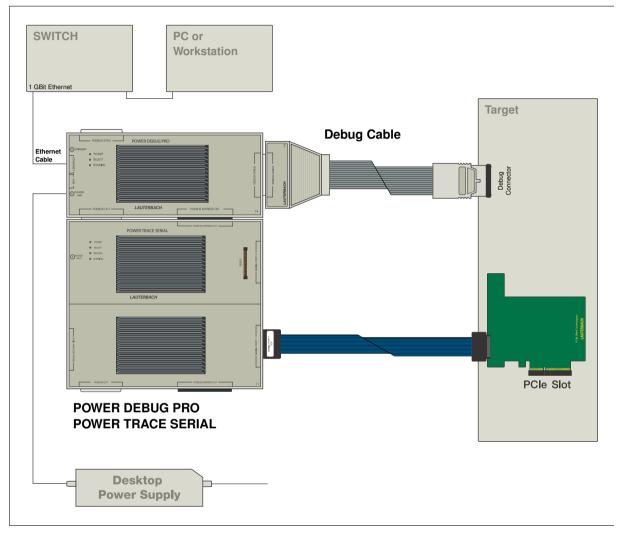

## **TRACE32 Debugger and Trace with PowerTrace Serial**

If you are interested in general information on PowerTrace Serial, please refer to "PowerTrace Serial User's Guide" (serialtrace\_user.pdf).

#### Aurora Traceport

The TRACE32 POWER TRACE SERIAL for the QorlQ has a 40-pin connector. If you are using a Power.org defined connector (22-, 46- or 70-pin) on your target you will need a fitting Aurora converter to connect TRACE32 POWER TRACE SERIAL.

All Lauterbach Aurora converters provide a JTAG connector and a Samtec40 connector for the tool side and a Power.org connector for the target side. Depending on your board design you have to use either:

- The board JTAG connector to connect the TRACE32 Debug Cable and the Lauterbach Aurora converter to connect TRACE32 POWER TRACE SERIAL.

- Or you use the Aurora converter to connect both, the TRACE32 Debug Cable and TRACE32 POWER TRACE SERIAL.

If your board does not provide an Aurora traceport, it is also possible to convey the NEXUS core trace information off-chip via the PCIe interface.

The TRACE32 POWER TRACE SERIAL for the QorlQ needs additionally a *TRACE32 License for PCI Express* in this case, and probably a *Lauterbach Slot-Card-Converter*.

# **Breakpoints**

There are two types of breakpoints available: ONCHIP breakpoints and SOFTware breakpoints.

| 👸 B::Break.List                                                                | ×   |

|--------------------------------------------------------------------------------|-----|

| 🗶 Delete All 🔘 Disable All 🔘 Enable All 🚫 Init 🖉 Method 😰 Store 😰 Load 📦 Set   |     |

| address type method                                                            |     |

| C:FFF90864 Program<br>C:FFF90860 Program<br>SOFT<br>V Ø ProcessDataExchange\28 | 4 > |

|                                                                                | ► a |

## **Software Breakpoints**

To set a software breakpoint, before resuming the CPU, the debugger replaces the instruction at the breakpoint address with a **DNH** instruction.

#### **On-chip Breakpoints**

To set breakpoints on code in read-only memory, only the on-chip instruction address breakpoints are available. With the command **MAP.BOnchip** *<range>* it is possible to declare memory address ranges for use with on-chip breakpoints to the debugger. The number of breakpoints is then limited by the number of available on-chip instruction address breakpoints.

- **On-chip breakpoints:** Total amount of available on-chip breakpoints.

- **Instruction address breakpoints:** Number of on-chip breakpoints that can be used to set program breakpoints into ROM/FLASH/EEPROM.

- Data address breakpoints: Number of on-chip breakpoints that can be used as Read or Write breakpoints.

| Core type                                                            | On-chip                                      | Instruction Address                                       | Data Address                                                                                                                                                                                                           |

|----------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (CPU types):                                                         | Breakpoints                                  | Breakpoints                                               | Breakpoints                                                                                                                                                                                                            |

| e500mc<br>(P204X,<br>P30XX,<br>P40XX),<br>e5500<br>(P5XXX,<br>T10XX) | 2 instruction<br>2 read/write<br>no counters | 2 single breakpoints<br>or<br>1 exact breakpoint<br>range | 2 single breakpoints<br>or<br>1 exact breakpoint range<br>or<br>2 ranges up to 4kB each<br>MAP.BOnchip (exact or<br>extended range)<br>or<br>1 range up to 4kB (exact or<br>extended range) and 1<br>single breakpoint |

| Core type                            | On-chip                                      | Instruction Address                                        | Data Address                                                                                                                                                                                            |

|--------------------------------------|----------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (CPU types):                         | Breakpoints                                  | Breakpoints                                                | Breakpoints                                                                                                                                                                                             |

| e6500<br>(T2XXX,<br>T4XXX,<br>B4XXX) | 8 instruction<br>2 read/write<br>no counters | 8 single breakpoints<br>or<br>4 exact breakpoint<br>ranges | 2 single breakpoints<br>or<br>1 exact breakpoint range<br>or<br>2 ranges up to 4kB each<br>(exact or extended range)<br>or<br>1 range up to 4kB (exact or<br>extended range) and 1<br>single breakpoint |

| NOTE: | • "exact or extended range": To use the increased number of data address breakpoint ranges with up to 4kB each, either <b>TrOnchip.CONVert</b> must be enabled or exact 4kB ranges must be used.                                                                                                                                        |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | • Setting on-chip breakpoints with physical (real) address (Access Class Attribute "A:") is possible to simplify the usage for 1:1 translations and the peripheral handling. In any case the resulting hardware address comparison is based on effective addresses, TRACE32 will not convert physical to logical (effective) addresses! |

You can see the currently set breakpoints with the command Break.List.

If no more on-chip breakpoints are available, you will get an error message when trying to set a new on-chip breakpoint.

#### **Breakpoints on Program Addresses**

The debugger sets software and on-chip breakpoints to the effective address. If a breakpoint is set on a program address, the debugger will first try to set a software breakpoint. If writing the software breakpoint fails (translation error or bus error), then an on-chip breakpoint will be set instead. If a memory range must not be written by the debugger, it can be declared for on-chip breakpoint usage using MAP.BOnchip. Alternatively, it is also possible to force a single breakpoint to on-chip using the command Break.Set with option /Onchip:

```

Map.BOnchip 0xF8000000--0xFFFFFFF ;use on-chip breakpoints in FLASH

Break.Set 0xFFFF064 ;debugger sets on-chip breakpoint

Break.Set my_func1 /Onchip ;debugger sets on-chip breakpoint

```

Breakpoints can be configured to stop if the break event occurred a given number of times. For all QorIQ CPUs no on-chip counter will be used.

```

;stop on the 20th call of function foo Break.Set foo /Onchip /COUNT 20.

```

#### **Breakpoints on Data Addresses**

Data address breakpoints cause a debug event when a certain address or address range is read or written by the core. A data address breakpoint to a single address has a granularity of 1 byte.

```

Break.Set 0xC3F80004 /Read ;break when core reads from 0xC3F80004

Break.Set 0xC3F80004 /Write ;break when core writes to 0xC3F80004

Break.Set 0xC3F80004 /ReadWrite ;break on read or write access

Break.Set 0xC3F80000--0xC3F80023 /Write ;break address range

```

Similar to program address breakpoints, data address breakpoints can be configured to stop if the break event occurred a given number of times:

;stop on the 8th write to arrayindex Break.Set arrayindex /Write /COUNT 20.

Data address breakpoint limitations:

- 1. The source of the data access (read and/or write) must be the core, as the data address breakpoints are part of the core. Any other accesses from on-chip or off-chip peripherals (DMA etc.) will not be recognized by the data address breakpoints.

- 2. The data being targeted must be qualified by an address in memory. It is not possible to set a data address breakpoint to GPR, SPR etc.

## **Breakpoints on Data Access at Program Address**

A normal data access breakpoint as described above hits on all data accesses to the memory address or address range, independent of the program address which caused the access. It is also possible to set a data address breakpoint which only hits if the access is performed from a specified program address. The specified program address must be a load or store instruction.

```

;Break if the instruction at address 0x40001148 reads from variable count

Break.Set 0x40001148 /MemoryRead count

;Break if the instruction at address 0x40001148 writes to range

Break.Set 0x40001148 /MemoryWrite 0xFFFFF000--0xFFFFFFFF

```

The program address can also be an address range or a range of debug symbols:

;Break on all accesses to count from code of the address range Break.Set 0x40000100--0x400001ff /MemoryReadWrite count ;Break if variable nMyIntVar is written by an interrupt handler ;(debug symbols IVORxx\_Handler loaded from debug symbols) Break.Set IVOR0\_Handler--IVOR15\_Handler /MemoryWrite nMyIntVar ;Break if variable nTestValue is written within function test\_func Break.Set sYmbol.RANGE(test\_func) /MemoryWrite nTestValue ;Break if variable nTestValue is written outside of test\_func Break.Set sYmbol.RANGE(test\_func) /Exclude /MemoryWrite nTestValue

#### **Breakpoints on Data Value**

The e500mc and e5500 cores do not support on-chip breakpoints on data values, but TRACE32 supports them by software emulation. When a data value breakpoint is set, the debugger will use one of the data address breakpoints. When the core hits that breakpoint, the target application will stop and the debugger will evaluate if the data value matches. If the value matches, the debugger will stop execution, if it does not match, the debugger will restart the application. Using software emulated data value breakpoints will cause the target application to slow down.

Examples for setting data value breakpoints:

;Break when the value 0x1233 is written to the 16-bit word at 0x40000200 Break.Set 0x40000200 /Write /Data.Word 0x1233 ;Break when a value **not equal 0x98** is written to the 8-bit variable xval Break.Set xval /Write /Data.Byte !0x98 ;Break when decimal 32-bit value 4000 is written ;to variable *count* within function *foo*

Break.Set sYmbol.RANGE(foo) /MemoryWrite count /Data.Long 4000.

Access classes are used to specify how TRACE32 PowerView accesses memory, registers of peripheral modules, addressable core resources, coprocessor registers and the TRACE32 Virtual Memory.

Addresses in TRACE32 PowerView consist of:

- An access class, which consists of one or more letters/numbers followed by a colon (:)

- A number that determines the actual address

Here are some examples:

| Command:                           | Effect:                                               |

|------------------------------------|-------------------------------------------------------|

| List.auto P:0x1000                 | Opens a List window displaying program memory         |

| Data.dump D:0xFF800000 /LONG       | Opens a DUMP window at <b>data</b> address 0xFF800000 |

| Data.Set SPR:415. %Long 0x00003300 | Write value 0x00003300 to the SPR IVOR15              |

| PRINT Data.Long(ANC:0xFFF00100)    | Print data value at physical address 0xFFF00100       |

## Access Classes to Memory and Memory Mapped Resources

The following memory access classes are available:

| Access Class | Description                                          |

|--------------|------------------------------------------------------|

| Р            | Program (memory as seen by core's instruction fetch) |

| D            | Data (memory as seen by core's data access)          |

| IC           | L1 Instruction Cache (or L1 Unified cache)           |

| DC           | L1 Data Cache                                        |

| L2           | L2 Cache                                             |

| NC           | No Cache (access with caching inhibited)             |

In addition to the access classes, there are access class attributes.

Examples:

| Command:                | Effect:                                                          |

|-------------------------|------------------------------------------------------------------|

| List.auto SP:0x1000     | Opens a List window, displaying <b>supervisor</b> program memory |

| Data.Set ED:0x3330 0x4F | Write 0x4F to address 0x3330 using real-time memory access       |

The following access class attributes are available:

| Access Class Attribute | Description                                                                                                                                                   |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E                      | Use real-time memory access                                                                                                                                   |

| A                      | Given address is physical (bypass MMU)                                                                                                                        |

| U                      | TS (translation space) == 1 (user memory)                                                                                                                     |

| S                      | TS (translation space) == 0 (supervisor memory)                                                                                                               |

| Н                      | Hypervisor privilege level based access.<br>The H access class is a generic placeholder for either the HS or the<br>HU access class or a combination of both. |

| HS                     | Hypervisor-supervisor access.<br>Access to supervisor memory with hypervisor privilege level.                                                                 |

| HU                     | Hypervisor-user access.<br>Access to user memory with hypervisor privilege level.                                                                             |

| G                      | Guest privilege level based access.<br>The G access class is a generic placeholder for either the GS or the<br>GU access class or a combination of both.      |

| GS                     | Guest-supervisor access.<br>Access to supervisor memory with guest privilege level.                                                                           |

| GU                     | Guest-user access.<br>Access to user memory with guest privilege level.                                                                                       |

If an access class attribute is specified without an access class, TRACE32 PowerView will automatically add the default access class of the used command. For example, **List.auto** U:0x100 will be expanded to **List.auto**UP:0x100.

The guest and hypervisor privilege level access classes H, HS, HU, G, GS and GU are important if **SYStem.Option.ZoneSPACES** is set to **ON**.

## Access Classes to Other Addressable Core and Peripheral Resources

The following access classes are used to access registers which are not mapped into the processor's memory address space.

| Access Class | Description                                                                        |

|--------------|------------------------------------------------------------------------------------|

| SPR          | Special Purpose Register (SPR) access                                              |

| PMR          | Performance Monitor Register (PMR) access                                          |

| DBG          | Special debug register access, e.g. Reset Configuration Word (RCW) register access |

SPR and PMR registers are addressed by specifying the register number after the access class.

The access class DBG, which covers a wide variety of accesses, has a special encoding. The encoding as listed below is valid only for the QorlQ debugger.

| DBG access mask | Description                                                                              |

|-----------------|------------------------------------------------------------------------------------------|

| DBG:0x0100000R  | Access to the 16 RCW registers to set another RCW before the (next) <b>SYStem.Up</b> .   |

|                 | R: Nexus register ID (0x0-0xF)                                                           |

|                 | For further details, please refer to <b>Programming the Reset</b><br>Configuration Word. |

## Cache

## **Memory Coherency**

The following table describes which memory will be updated depending on the selected access class:

| Access Class | D-Cache     | I-Cache     | L2 Cache    | Memory (uncached) |

|--------------|-------------|-------------|-------------|-------------------|

| DC:          | updated     | not updated | not updated | not updated       |

| IC:          | not updated | updated     | not updated | not updated       |

| L2:          | not updated | not updated | updated     | not updated       |

| NC:          | not updated | not updated | not updated | updated           |

| D:           | updated     | not updated | updated     | updated           |

| P:           | not updated | updated (*) | updated     | updated           |

(\*) Depending on the debugger configuration, the coherency of the instruction cache will not be achieved by updating the instruction cache, but by invalidating the instruction cache. See **SYStem.Option.ICFLUSH** for details.

The data cache logic of Power Architecture cores is described as states of the MESI protocol. The combinations for the MESI states are just available for DC and the unified L2 cache and thus the MESI state is just displayed for these cache windows in the column "#".

State translation table:

| MESI state (#) | Flag                   |  |  |  |  |  |

|----------------|------------------------|--|--|--|--|--|

| M (modified)   | V(alid) && D(irty)     |  |  |  |  |  |

| E (exclusive)  | V(alid) && NOT D(irty) |  |  |  |  |  |

| S (shared)     | V(alid) && S(hared)    |  |  |  |  |  |

| l (invalid)    | NOT V(alid)            |  |  |  |  |  |

The debugger also displays the cache state using the following cache line status flags:

- **v**alid (IC, DC, L2)

- locked (IC, DC, L2)

- dirty (DC, L2)

- shared (DC, L2)

- **n**oncoherent (L2)

- cast-out (DC)

- plr**u** (IC, DC, L2)

## **Viewing Cache Contents**

The cache contents can be viewed using the CACHE.DUMP command.

| ;Command   |    | ; | Cache                |

|------------|----|---|----------------------|

| CACHE.DUMP | IC | ; | L1 instruction cache |

| CACHE.DUMP | DC | ; | L1 data dache        |

| CACHE.DUMP | L2 | ; | L2 (unified cache)   |

| Í | 🛱 B::cache.dump IC |      |     |     |     |          |          |          |          |          |          |          |     |          |

|---|--------------------|------|-----|-----|-----|----------|----------|----------|----------|----------|----------|----------|-----|----------|

|   | address            | set  | way | V   | u   | 00       | 04       | 08       | 0C       | 10       | 14       | 18       | 1   | 5        |

|   | A:0:0003C000       | 0000 | 00  | ٧ - | - 0 | 801D00A8 | 7C002214 | 901D00A8 | 7C2004AC | 93DD00BC | 4BFFFF6C | 60000000 | 6   | ~        |

|   | A:0:0000C000       | 0000 | 01  | V - | - 0 | 7C002378 | 7C00492D | 40A2FFF4 | 800B0004 | 5400017E | 7C00019C | 80010034 | В   |          |

|   | A:0:00037000       | 0000 | 02  | V - | - 0 | 4BFFFFA0 | 409E000C | 2B8803FF | 419DFFAC | 38E00000 | 39000400 | 4BFFFFA0 | 3   |          |

|   | A:0:00048000       | 0000 | 03  | V - | - 0 | 4803D7E1 | 807F0008 | 4BFF4D59 | 2F830000 | 419E0024 | 801F000C | 5409016F | 4 1 | <b>7</b> |

|   |                    | •    |     |     | 11  | I        |          |          |          |          |          |          | ۴., | H        |

|   |                    |      |     |     |     |          |          |          |          |          |          |          |     |          |

| III Bi:cache.dump DC |      |      |     |   |   |     |     |     |     |          | 3        |          |          |          |          |    |   |

|----------------------|------|------|-----|---|---|-----|-----|-----|-----|----------|----------|----------|----------|----------|----------|----|---|

| add                  | ress | set  | way | # | v | 1.  | d : | 5 ( | сu  | 00       | 04       | 08       | 0C       | 10       | 14       | 18 |   |

| A:0:0307             | 13C0 | 000F | 03  | E | V |     | -   |     | - 4 | FFFFF10  | FFFFFF1B | 01000100 | C06A6440 | 00000040 | 00000000 | C3 |   |

| A:0:006D             |      |      |     | I | - |     |     |     |     |          |          |          |          |          |          |    | _ |

| A:0:0069             | B3C0 | 000F | 05  | Е | V |     | -   |     | - 4 |          | 00000000 |          |          |          |          |    |   |

| A:0:005C             |      |      |     | E | V |     | -   |     | - 4 |          | 00656E00 |          |          |          |          |    |   |

| A:0:0055             | A3C0 | 000F | 07  | Е | V |     | -   | - ( | C 4 | 63AA0132 | 04546162 | 7308546B | E3D0C828 | F7C90454 | 8ADAF510 | 54 | Ŧ |

|                      |      | 4    |     |   |   | - 1 | 11  |     |     |          |          |          |          |          |          | •  |   |

| III B::cache.dump L2 |       |     |        |       |     |          |          |          |          |          | ×        |                        |

|----------------------|-------|-----|--------|-------|-----|----------|----------|----------|----------|----------|----------|------------------------|

| address              | set w | vay | #v10   | 51    | าน  | 00       | 04       | 08       | 0C       | 10       | 14       | 18                     |

| A:0:0003C080         | 0002  | 02  | EV     | 1     | 0 1 | 7C002A14 | 7CC93214 | 901F017C | 2F9C0000 | 90DF0184 | 409E0014 | 83                     |

| A:0:2B860080         | 0002  | 03  | MV - E | )     | - 0 | 0000000A | 000000B  | 000000C  | FFFFFFF  | 00000001 | 00000000 | EB                     |

| A:0:006D8080         | 0002  | 04  | 5 V    | - S - | - 0 | EFD02000 | EFCFC000 | EFD24000 | EFD1E000 | EFD18000 | EFD12000 | EF                     |

| A:0:2BC08080         | 0002  | 05  | MV- 0  | ) (   | - 0 | 00000036 | 00000036 | 0000001B | 00000001 | 00000000 | EB8CE0D0 | EB                     |

| A:0:00058080         | 0002  | 06  | EV     | 1     | 0 0 | 3D60C06E | 5463103A | 396B835C | 7CA42B78 | 7C0B182E | 7D234B78 | 7C 🔻                   |

|                      | •     |     |        |       |     |          |          |          |          |          |          | <ul> <li>Id</li> </ul> |

| -                    |       |     |        |       |     |          |          |          |          |          |          |                        |

|                      |       |     |        | Α     |     |          |          |          | В        |          |          |                        |

- A MESI state, cache line status bits

- B Cache line data

The meaning of the data fields in the **CACHE.DUMP** windows is explained in the following table:

| Data field             | Meaning                                                                                                                                        |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| address                | Physical address of the cache line. The address is composed of cache tag and set index.                                                        |

| set<br>way             | Set and way index of the cache                                                                                                                 |

| #, v, l, d, s, n, c, u | Status bits of the cache line: # (MESI state), v(alid), l(ocked), d(irty), s(hared), n(oncoherent), c(ast-out), (pseudo least recently) u(sed) |

| 00 04 08               | Address offsets within cache line corresponding to the cached data                                                                             |

| address (right field)  | Debug symbol assigned to address                                                                                                               |

## **Multicore Debugging**

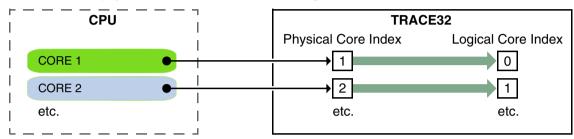

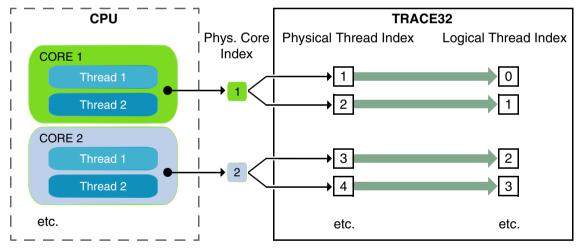

#### **General Information**

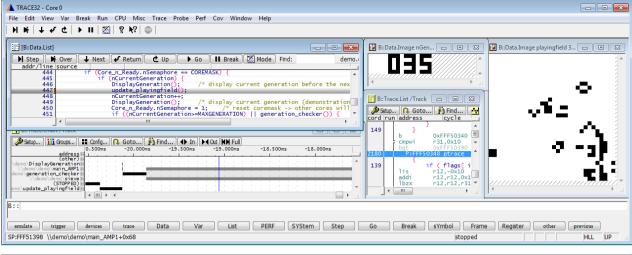

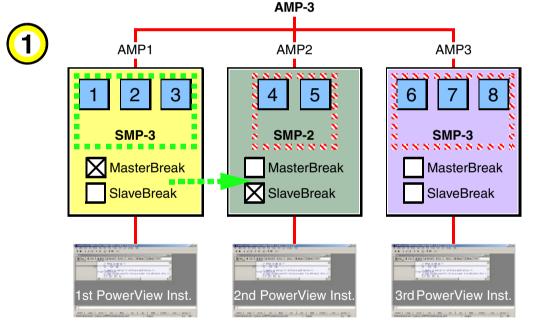

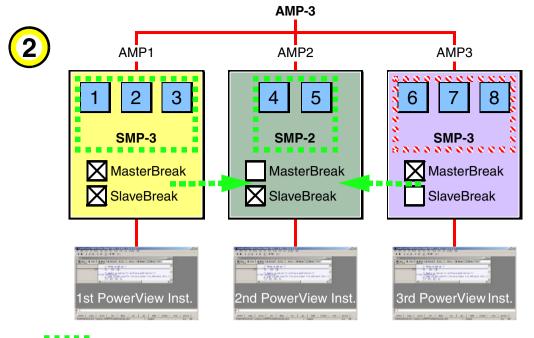

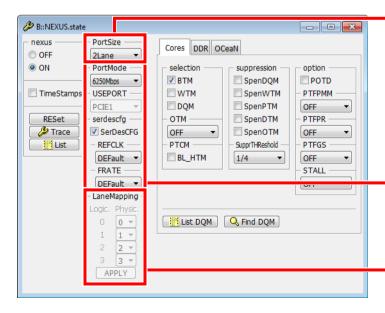

All QorlQ processors contain multiple cores that can be debugged as an **SMP** or an **AMP** system configuration. After the CPU has been selected, all physical cores / physical threads are assigned to this TRACE32 instance per default. The user can then choose which **logical core is displayed by TRACE32**. The resulting relationship between physical and logical cores is shown below:

• Processors with physical e500mc and e5500 cores, e.g. P4080:

• Processors with physical e6500 cores and physical threads, e.g. T2080:

To choose a physical core or physical thread, you have the following options:

- Open the TargetSystem.state window, and double-click the logical core.

- Open the **CORE.SHOWACTIVE** window, and click the logical core.

- Right-click the status line core number box to display the list of logical cores, and click the logical core you want.

- Use the **CORE.select** < *logical\_core\_index* > command.

TRACE32 handles cores and threads with a unique TRACE32 instance related logical number.

Example for the T2080 processor with e6500 cores including two physical threads for each physical core:

| ▲ B::TargetSystem.state                                                                           |               |                                                                |     |

|---------------------------------------------------------------------------------------------------|---------------|----------------------------------------------------------------|-----|