# ARC Debugger and Trace

Release 09.2023

## **ARC Debugger and Trace**

## **TRACE32 Online Help**

**TRACE32 Directory**

**TRACE32 Index**

| TRACE32 Documents                                                                                                                                                                   |                                                                                                                                                                                    |                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| ICD In-Circuit Debugger                                                                                                                                                             |                                                                                                                                                                                    |                                  |

| Processor Architecture Manuals                                                                                                                                                      |                                                                                                                                                                                    |                                  |

| ARC                                                                                                                                                                                 |                                                                                                                                                                                    |                                  |

| ARC Debugger and Trace                                                                                                                                                              |                                                                                                                                                                                    | 1                                |

| History                                                                                                                                                                             |                                                                                                                                                                                    | 6                                |

| Introduction Supported ARC Cores Brief Overview of Documents for New Demo and Start-up Scripts                                                                                      | v Users                                                                                                                                                                            | <b>7</b><br>7<br>7<br>9          |

| Warning                                                                                                                                                                             |                                                                                                                                                                                    | 10                               |

| Troubleshooting                                                                                                                                                                     |                                                                                                                                                                                    | <b>11</b><br>11                  |

| FAQ                                                                                                                                                                                 |                                                                                                                                                                                    | 11                               |

| Quick Start                                                                                                                                                                         |                                                                                                                                                                                    | 12                               |

| CPU specific SETUP Command SETUP.DIS                                                                                                                                                | Disassembler configuration                                                                                                                                                         | <b>16</b>                        |

| CPU specific SYStem Commands                                                                                                                                                        |                                                                                                                                                                                    | 17                               |

| SYStem.CONFIG.state SYStem.CONFIG <pre><pre><pre><pre><pre><pre><pre><pre></pre></pre></pre></pre></pre></pre></pre></pre>                                                          |                                                                                                                                                                                    | 17<br>19<br>21                   |

| <parameters> describing the "JTAG MultiTap      <parameters> configuring a CoreSig      <parameters> describing debug and Multicore Examples</parameters></parameters></parameters> | ght Debug Access Port "DAP"                                                                                                                                                        | 25<br>27<br>28<br>30<br>35       |

| SYStem.CPU SYStem.JtagClock SYStem.LOCK SYStem.MemAccess SYStem.Mode SYStem.Option                                                                                                  | Select CPU type Select clock for JTAG communication Lock and tristate the debug port Real-time memory access (non-intrusive) Select target reset mode Set a target-specific option | 36<br>37<br>39<br>39<br>41<br>43 |

|                                                                                                                                                                                     |                                                                                                                                                                                    |                                  |

| SYStem.Option.AHBHPROT           | Select AHB-AP HPROT bits                         | 43 |

|----------------------------------|--------------------------------------------------|----|

| SYStem.Option.AXIACEEnable       | ACE enable flag of the AXI-AP                    | 43 |

| SYStem.Option.AXICACHEFLAGS      | Configure AXI-AP cache bits                      | 44 |

| SYStem.Option.AXIHPROT           | Select AXI-AP HPROT bits                         | 45 |

| SYStem.Option.CorePowerDetection | Set methods to detect core power                 | 45 |

| SYStem.Option.DAPDBGPWRUPREC     | Force debug power in DAP                         | 47 |

| SYStem.Option.DAPREMAP           | Rearrange DAP memory map                         | 48 |

| SYStem.Option.DAPSYSPWRUPREC     | Force system power in DAP                        | 48 |

| SYStem.Option.DAPNOIRCHECK       | No DAP instruction register check                | 49 |

| SYStem.Option.DCFLUSH            | Invalidate/flush data-cache for modified memory  | 49 |

| SYStem.Option.DEBUGPORTOptions   | Options for debug port handling                  | 49 |

| SYStem.Option.detectOTrace       | Disable auto-detection of on-chip trace          | 50 |

| SYStem.Option.Endianness         | Set the target endianness                        | 51 |

| SYStem.Option.EnReset            | Allow the debugger to drive nRESET (nSRST)       | 51 |

| SYStem.Option.HotBreakPoints     | Set breakp. when CPU is running                  | 52 |

| SYStem.Option.ICFLUSH            | Invalidate instruction-cache for modified memory | 52 |

| SYStem.Option.IMASKASM           | Disable interrupts while single stepping         | 53 |

| SYStem.Option.IMASKHLL           | Disable interrupts while HLL single stepping     | 53 |

| SYStem.Option.IntelSOC           | Core is part of Intel® SoC                       | 53 |

| SYStem.Option.LimmBreakPoints    | Software breakpoints with extra NOPs             | 54 |

| SYStem.Option.MMUSPACES          | Separate address spaces by space IDs             | 54 |

| SYStem.Option.OVERLAY            | Enable overlay support                           | 55 |

| SYStem.Option.RegNames           | Enable trivial names for core registers          | 56 |

| SYStem.Option.PowerDetection     | Choose method to detect the target power         | 56 |

| SYStem.Option.ResetDetection     | Choose method to detect a target reset           | 57 |

| SYStem.Option.TIMEOUT            | Define maximum time for core response            | 57 |

| SYStem.Option.TRST               | Allow debugger to drive TRST                     | 58 |

| SYStem.POWER                     | Control target power                             | 58 |

| SYStem.state                     | Show SYStem settings window                      | 58 |

| On-chip Breakpoints/Actionpoints |                                                  | 59 |

| Using On-chip Breakpoints        |                                                  | 59 |

| Breakpoints in a ROM Area        |                                                  | 59 |

| Limitations                      |                                                  | 60 |

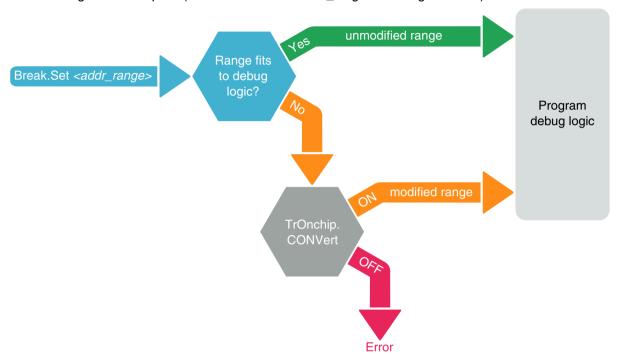

| TrOnchip.CONVert                 | Allow extension of address range of breakpoint   | 61 |

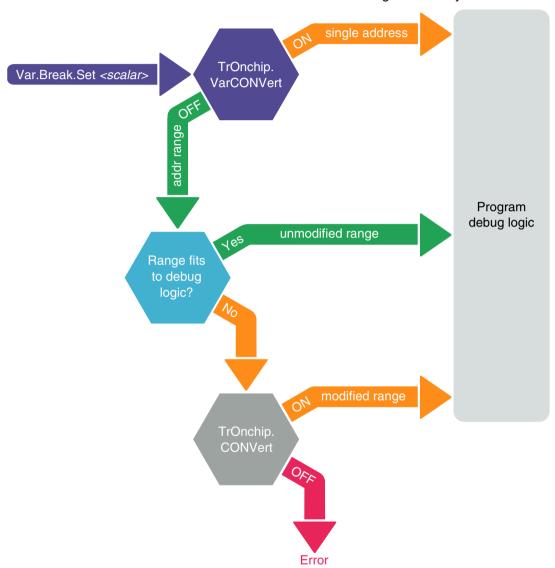

| TrOnchip.VarCONVert              | Convert breakpoints on scalar variables          | 63 |

| TrOnchip.OnchipBP                | Number of on-chip breakpoints used by debugger   | 64 |

| TrOnchip.RESet                   | Set on-chip trigger to default state             | 65 |

| TrOnchip.state                   | Display on-chip trigger window                   | 65 |

| CPU specific MMU Commands        |                                                  | 66 |

| MMU.DUMP                         | Page wise display of MMU translation table       | 66 |

| MMU.List                         | Compact display of MMU translation table         | 68 |

| MMU.SCAN                         | Load MMU table from CPU                          | 69 |

| MMU.Init                         | Invalidate TLB entries                           | 70 |

©1989-2023 Lauterbach ARC Debugger and Trace | 3

| MMU.Set                                | Set an MMU TLB entry                                   | 70 |

|----------------------------------------|--------------------------------------------------------|----|

| CPU specific JTAG.CONFIG Comm          | nands                                                  | 71 |

| JTAG.CONFIG                            | Electrical characteristics of MIPI-60 debug signals    | 7  |

| JTAG.CONFIG.DRiVer                     | Set slew rate of JTAG signals                          | 7  |

| JTAG.CONFIG.PowerDownTriState          | e Automatically tristate outputs                       | 72 |

| JTAG.CONFIG.TckRun                     | Free-running TCK mode                                  | 72 |

| JTAG.CONFIG.TDOEdge                    | Select TCK edge                                        | 72 |

| JTAG.CONFIG.Voltage.HooKTHres          | shold Set hook threshold voltages                      | 73 |

| JTAG.CONFIG.Voltage.THreshold          | Set JTAG threshold voltages                            | 73 |

| JTAG.CONFIG.Voltage.REFerence          | Voltage level of signals send to target                | 74 |

| Trace specific NEXUS Commands          |                                                        | 7  |

| NEXUS.AuxTM                            | Enable auxiliary register trace messages               | 75 |

| NEXUS.BTM                              | Enable program trace messaging                         | 75 |

| NEXUS.CLOCK                            | Clock to calculate time out of cycle count information | 76 |

| NEXUS.DataSuppress                     | Suppress data flow on likely FIFO overflow             | 76 |

| NEXUS.DDR                              | Enable NEXUS double data rate mode                     | 76 |

| NEXUS.DSM                              | Enable core debug status messages                      | 7  |

| NEXUS.DTM                              | Enable data trace messages                             | 7  |

| NEXUS.FILTER                           | Configure the onchip trace filter resources            | 78 |

| NEXUS.FILTER.ACompLimit                | Trace address filters used by debugger                 | 78 |

| NEXUS.FILTER.DCompLimit                | Number of trace data filter used by debugger           | 78 |

| NEXUS.HISToryTHreshold                 | Control the conditional history threshold              | 79 |

| NEXUS.OFF                              | Switch the NEXUS trace port off                        | 79 |

| NEXUS.ON                               | Switch the NEXUS trace port on                         | 79 |

| NEXUS.PortMode                         | Set NEXUS trace port frequency                         | 80 |

| NEXUS.Register                         | Display NEXUS trace control registers                  | 80 |

| NEXUS.RegTM                            | Enable core register trace messages                    | 80 |

| NEXUS.RESet                            | Reset NEXUS settings                                   | 80 |

| NEXUS.RTTBUILD                         | Define build configuration of used DesignWare trace    | 8  |

| NEXUS.STALL                            | Stall program execution when FIFO full                 | 8  |

| NEXUS.state                            | Display NEXUS port configuration dialog                | 8  |

| NEXUS.SyncFrame                        | Control SYNC frame insertion in ATB stream             | 8  |

| NEXUS.TImeMode                         | Select method of time measurement                      | 82 |

| NEXUS.TimeStampCLOCK                   | Specify frequency of the global timestamp              | 83 |

| NEXUS.TraceID                          | Set ID for CoreSight ATB stream                        | 84 |

| NEXUS.WTM                              | Enable watchpoint trace messages                       | 84 |

| <b>Debug Connector Type and Pinout</b> |                                                        | 8  |

| Normal 20-Pin Connector                |                                                        | 8  |

| MIPI10 / MIPI20 / MIPI34 Connecto      | or                                                     | 87 |

| Converged MIPI60-Cv2 Connector         |                                                        | 87 |

| XDP Connector                          |                                                        | 87 |

| Trace Connector Type and Pinout        |                                                        | 88 |

©1989-2023 Lauterbach

| Trace Signals                                   | 88 |

|-------------------------------------------------|----|

| Normal Nexus Auxiliary Port (Mictor 38)         | 89 |

| Dual Eight-bit Nexus Auxiliary Port (Mictor 38) | 90 |

| Out Offload and CoreSight TPIU                  | 90 |

©1989-2023 Lauterbach

## **ARC Debugger and Trace**

## Version 10-Oct-2023

## History

| 16-Jun-23 | Chapter 'Legacy MIPI60-C Connector' was removed.                                     |

|-----------|--------------------------------------------------------------------------------------|

| 17-Jan-23 | Added SETUP.DIS command.                                                             |

| 20-Jul-22 | For the MMU.SCAN ALL command, CLEAR is now possible as an optional second parameter. |

| 07-Jun-22 | New command: JTAG.CONFIG.TckRun.                                                     |

| 17-Feb-22 | New command SYStem.Option.TRST.                                                      |

## Introduction

This document describes the processor-specific settings and features of the ARC in-circuit debugger.

Please keep in mind that only the **Processor Architecture Manual** (the document you are reading at the moment) is CPU specific, while all other parts of the online help are generic for all CPUs supported by Lauterbach. So if there are questions related to the CPU, the Processor Architecture Manual should be your first choice.

## **Supported ARC Cores**

The following ARC cores from Synopsys, Virage Logic or ARC International are supported:

- ARC Vector DSPs: EV7x, EV7xFS, VPX2/VPX3/VPX5, VPX2FS/VPX3FS/VPX5FS

- ARC-HS family: HS34, HS36, HS38, HS44, HS45D, HS46FS, HS47D, HS47DFS, HS48, HS48FS

- ARC-EM family: EM4, EM5D, EM6, EM7D, EM9D, EM11D, EM22FS

- ARC 700 core family: ARC710D, ARC725D, ARC750D, ARC770D

- ARC 600 core family: ARC601, ARC605, ARC610D, ARC652D, ARC630D, AS211SFX, AS221BD

- ARCtangent-A5 cores

- ARCtangent-A4 cores

#### **Brief Overview of Documents for New Users**

#### **Architecture-independent information:**

- "Training Basic Debugging" (training\_debugger.pdf): Get familiar with the basic features of a TRACE32 debugger.

- "T32Start" (app\_t32start.pdf): T32Start assists you in starting TRACE32 PowerView instances for different configurations of the debugger. T32Start is only available for Windows.

- "General Commands" (general ref <x>.pdf): Alphabetic list of debug commands.

#### **Architecture-specific information:**

• "Processor Architecture Manuals": These manuals describe commands that are specific for the processor architecture supported by your Debug Cable. To access the manual for your processor architecture, proceed as follows:

- Choose **Help** menu > **Processor Architecture Manual**.

- "OS Awareness Manuals" (rtos\_<os>.pdf): TRACE32 PowerView can be extended for operating system-aware debugging. The appropriate OS Awareness manual informs you how to enable the OS-aware debugging.

To get started with the most important manuals, use the Welcome to TRACE32! dialog (WELCOME.view):

©1989-2023 Lauterbach ARC Debugger and Trace | 8

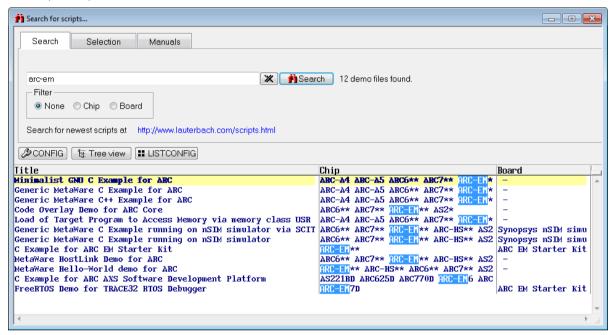

## **Demo and Start-up Scripts**

Lauterbach provides ready-to-run PRACTICE start-up scripts and examples.

#### To search for PRACTICE scripts, do one of the following in TRACE32 PowerView:

- Type at the command line: WELCOME.SCRIPTS

- or choose File menu > Search for Script.

You can now search the demo folder and its subdirectories for PRACTICE start-up scripts (\*.cmm) and other demo software.

You can also manually navigate in the ~~/demo/arc/ subfolder of the system directory of TRACE32.

#### WARNING:

To prevent debugger and target from damage it is recommended to connect or disconnect the Debug Cable only while the target power is OFF.

#### Recommendation for the software start:

- 1. Disconnect the Debug Cable from the target while the target power is off.

- 2. Connect the host system, the TRACE32 hardware and the Debug Cable.

- 3. Power ON the TRACE32 hardware.

- 4. Start the TRACE32 software to load the debugger firmware.

- Connect the Debug Cable to the target. 5.

- 6. Switch the target power ON.

- 7. Configure your debugger e.g. via a start-up script.

#### Power down:

- 1. Switch off the target power.

- 2. Disconnect the Debug Cable from the target.

- 3. Close the TRACE32 software.

- 4. Power OFF the TRACE32 hardware.

## **Troubleshooting**

The LAUTERBACH debug module LA-7701 "DEBUG INTERFACE" is not supported.

You require a Power Debug module (e.g. LA-7702, LA-7704, LA-7705, LA-7707, LA-7708, LA-7690, LA-7699)

## **SYStem.Up Errors**

The SYStem.UP command is the first command of a debug session where communication with the target is required. If you receive error messages while executing this command this may have the following reasons.

- The target has no power.

- A FPGA which could hold an ARC Core like an ARCangel, is not loaded yet or does not contain an ARC Core with a debugging interface.

- There is a problem with the electrical connection between the debugger and the target check if the JTAG connector is plugged correctly and if the target is built corresponding to the definition of the used JTAG connector.

### **FAQ**

Please refer to https://support.lauterbach.com/kb.

## **Quick Start**

This chapter should help you to prepare your debugger for ARC. Depending on your application not all steps might be necessary.

For some applications additional steps might be necessary, that are not described in this Quick Start section.

#### 1. Prepare the Start

Connect the Debug Cable to your target. Check the orientation of the connector. Pin 1 of the debug cable is marked with a small triangle next to the nose of the target **connector**.

Power up your TRACE32 system.

Start the TRACE32 Debugger Software.

Power up your Target!

To prevent damage please take care to follow this sequence all the time you are preparing a start.

## 2. Select the CPU Type

For example:

SYStem.CPU ARC-HS

If you have a normal ARC core without the need of special configurations (e.g. position inside a JTAG daisy chain) you can also use the keyword AUTO. E.g.:

SYStem.CPU AUTO

## 3. Set the speed of the JTAG debug clock

You can select the JTAG clock frequency, which the Debugger uses to communicate with the target. This can be either done in the JtagClock field in the SYStem window, or by using the command line with the command SYStem.JtagClock. The maximum clock frequency might depend on the configuration of your FPGA design. The default clock frequency is 1 MHz.

#### 4. Configure the JTAG debug accesses

If you have a single ARC core and you use standard JTAG (IEEE 1149.1) there is nothing you have to do in this step.

#### Configure a multi-core setup

If you have more than one CPU core connected to the same JTAG port, please tell the debugger how it should connect to the core you want to debug:

In case of a JTAG daisy chain use command SYStem.DETECT SHOWChain to scan the chain. The result is shown in a window. Double-click on the desired core to tell the debugger which core you'd like to debug.

To configure the position of your core in the JTAG daisy chain manually use commands SYStem.CONFIG IRPOST. SYStem.CONFIG IRPRE. SYStem.CONFIG DRPOST and SYStem.CONFIG DRPRE.

In case your CPU is designed in the mature ARC MADI multicore configuration, please use command SYStem.CONFIG MADI to specify the core you want to debug.

#### **Configure Compact-JTAG**

Some ARC cores must be debugged via a two-wire debug interface called Compact-JTAG, cJTAG or IFFF 1149 7

Use command SYStem.CONFIG DEBUGPORTTYPE CJTAG to enable two wire mode. Add command SYStem.CONFIG CJTAGFLAGS 0x03 to skip TCA-scanning and to use TRACE32pseudo-keeper to workaround problems with the cJTAG implementation of your core.

## 5. Enter Debug Mode

```

; Connect to ARC core, stop the core and

SYStem.Up

jump to reset vector

```

This command resets the CPU, enters debug mode and jumps to the break address of the debugged core. After this command is executed, it is possible to access memory and registers.

## 6. Load your Application Program

When the core is prepared the code can be downloaded. This can be done with the command Data.Load.<file format> <file>.

```

Data.Load.Elf <file>.elf

; load application file

```

The options of the Data.LOAD command depend on the file format generated by the compiler. A detailed description of the Data.LOAD command is given in "General Commands Reference".

#### 7. Initialize Program Counter and Stackpointer (if required)

In a ready-to-run compiled ELF file, these settings are in the start-up code of the ELF file. In this case nothing has to be done. You can check the contents of Program Counter and Stack Pointer in the Register window, which provides the contents of all CPU Registers. Use CPU Registers in the CPU menu to open this window or use the command Register.

The Program Counter and the Stackpointer and all other registers can be set with the commands Register.Set PC <value> and Register.Set SP <value>. Here is an example of how to use these commands:

```

Register.Set PC 0xc000

; Set the Program Counter to address 0xC000

Register.Set SP 0xbff

; Set the Stack Pointer to address Oxbff

Register.Set PC main

; Set the PC to a label (here: function main)

```

#### 8. View the Source Code

Use the command **Data.List** to view the source code at the location of the Program Counter.

Now the guick start is done. If you were successful you can start to debug.

To reach the main() function use command GO main

### 10. Create a PRACTICE Script

LAUTERBACH recommends to prepare a PRACTICE script (\*.cmm, ASCII file format) to be able to do all the necessary actions with only one command. Here is a typical start sequence:

```

WinClear

: Clear all windows

SYStem.Reset

; Set all options in the SYStem window

: to default values

SYStem.CPU ARC700

; Use generic ARC700 core support.

System.JtagClock 5.MHz

; Set JTAG clock speed.

SYStem.Up

; Reset the target and enter debug mode

Data.LOAD.Elf demo.elf

; Load the application

Data.List

; Open disassembly window

Register.view

; Open register window

Var.Frame /Args /Locals

; Show call stack

; Auto-watch local variables

Var.Ref %HEX %DECIMAL

Break.Set 0x400

; Set software breakpoint on address

; 0x400

; Set software breakpoint on address of

Break.Set main

; main function.

```

For information about how to build a PRACTICE script file (\*.cmm file), refer to "Training Basic Debugging" (training debugger.pdf). There you can also find some information on basic actions with the debugger.

## Disassembler configuration

#### **SETUP.DIS**

Format: **SETUP.DIS** [<fields> [<bar>]] [<constants>] [<keywords>]

<keywords>: [RegNames | Generic]

[AddressOffset.auto | AddressOffset.Signed | AddressOffset.Unsinged]

Sets default values for configuring the disassembler output of newly opened windows. Affected windows and commands are List.Asm, Register.view, and Register.Set.

The command does not affect existing windows containing disassembler output.

| <fields>, <bar>,<br/><constants></constants></bar></fields> | For a description of the generic arguments, see <b>SETUP.DIS</b> in <b>general_ref_s.pdf</b> .                                                                                                                                                                                                                    |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RegNames<br>(default)                                       | Use the <i>ABI</i> (application binary interface) naming scheme for the names of the ARC general purpose registers (e.g. "sp" instead of "r28" for the stack pointer.).  This setting is equivalent with SYStem.Option.RegNames ON.                                                                               |

| Generic                                                     | Use the <i>register number</i> (x0, x1,, x31) naming scheme for the names of the ARC general purpose registers. (e.g. "r28" instead of "sp" for the stack pointer.).  This setting is equivalent with SYStem.Option.RegNames OFF.                                                                                 |

| AddressOffset.auto<br>(default)                             | Automatically choose a probably suitable format for the address offsets in load and store instructions. E.g.: For LD <dst>, [<reg>, <offset>] the offset is displayed as a signed number if the offset is smaller +/- 255 of if reg is gp/fp/sp/pcl, or as an unsigned hex-number otherwise.</offset></reg></dst> |

| AddressOff-<br>set.Signed                                   | Force the display of the address offsets in load and store instructions as signed. E.g.: For LD <dst>, [<reg>, <offset>] the offset is always displayed as a signed number.</offset></reg></dst>                                                                                                                  |

| AddressOff-<br>set.Unsinged                                 | Force the display of the address offsets in load and store instructions as unsigned. E.g.: For LD <dst>, [<reg>, <offset>] the offset is always displayed as a unsigned hexadecimal number.</offset></reg></dst>                                                                                                  |

#### SYStem.CONFIG.state

## Display target configuration

Format: SYStem.CONFIG.state [/<tab>]

DebugPort | Jtag | MultiTap | DAP | COmponents <tab>:

Opens the SYStem.CONFIG.state window, where you can view and modify most of the target configuration settings. The configuration settings tell the debugger how to communicate with the chip on the target board and how to access the on-chip debug and trace facilities in order to accomplish the debugger's operations.

Alternatively, you can modify the target configuration settings via the TRACE32 command line with the SYStem.CONFIG commands. Note that the command line provides additional SYStem.CONFIG commands for settings that are not included in the SYStem.CONFIG.state window.

| <tab></tab> | Opens the SYStem.CONFIG.state window on the specified tab. For tab descriptions, see below.                                                                                                                                                                                                                                |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DebugPort   | Informs the debugger about the debug connector type and the communication protocol it shall use.                                                                                                                                                                                                                           |

| Jtag        | Informs the debugger about the position of the Test Access Ports (TAP) in the JTAG chain which the debugger needs to talk to in order to access the debug and trace facilities on the chip.                                                                                                                                |

| MultiTap    | Informs the debugger about the existence and type of a System/Chip Level Test Access Port. The debugger might need to control it in order to reconfigure the JTAG chain or to control power, clock, reset, and security of different chip components.  For descriptions of the commands on the MultiTap tab, see MultiTap. |

| DAP         | Informs the debugger about an ARM CoreSight Debug Access Port (DAP) and about how to control the DAP to access chip-internal memory busses (AHB, APB, AXI) or chip-internal JTAG interfaces.                                                                                                                               |

#### **COmponents**

Informs the debugger about the existence and interconnection of on-chip CoreSight debug and trace modules and informs the debugger on which memory bus and at which base address the debugger can find the control registers of the modules.

This is only relevant in case used ARC core is debugged over a CoreSight DAP.

For descriptions of the commands on the COmponents tab, see COmponents in "Arm Debugger" (debugger\_arm.pdf).

©1989-2023 Lauterbach

ARC Debugger and Trace | 18

Format: SYStem.CONFIG.<sub cmd> <parameter>

**SYStem.MultiCore.**<*sub cmd>* <*parameter>* (deprecated)

CONNECTOR [MIPI34 | MIPI20T] <sub cmd>:

(DebugPort) CORE <core> <chip> CoreNumber < number>

DEBUGPORT [DebugCable0 | DebugCableA | DebugCableB]

**DEBUGPORTTYPE** [JTAG | SWD | CJTAG]

Slave [ON | OFF] TriState [ON | OFF]

MADI <id>

CJTAGFLAGS < flags> CJTAGTCA <value> SWDP [ON | OFF]

SWDPIdleHigh [ON | OFF] SWDPTargetSel <value>

<sub cmd>: **DAPDRPOST** <br/>

<br/>

bits> (JTAG) **DAPDRPRE** <br/>

<br/>

bits>

> **DAPIRPOST** < bits> **DAPIRPRE** <br/>

> <br/>

> bits> **DRPRE** <br/>

> <br/>

> bits> DRPOST <br/>

> <br/>

> bits> IRPRE <bits> IRPOST <bits> Slave [ON | OFF] TriState [ON | OFF] **TAPState** <state> TCKLevel [0 | 1]

<sub\_cmd>: AHBACCESSPORT <port> (DAP) APBACCESSPORT <port>

> **AXIACCESSPORT** <port> **DEBUGACCESSPORT** <port> **COREJTAGPORT** <port> JTAGACCESSPORT <port>

<sub\_cmd>: **MULTITAP [NONE | PrimaryTAP** <args> | JtagSEQuence.<sub\_cmd>]

(MultiTap)

(COmponents) COREDEBUG.RESet COREDEBUG.view

ETB.Base <address>

ETB.Name <string>

ETB.NoFlush [ON | OFF]

ETB.RESet ETB.Size <size>

ETB.STackMode [NotAvailbale | TRGETM | FULLTIDRM | NOTSET | FULL STOP | FULLCTI]

ETB.view

ETF.Base <address>

ETF.Name <string>

ETF.NoFlush [ON | OFF]

ETF.RESet ETF.Size <size>

ETF.STackMode [NotAvailbale | TRGETM | FULLTIDRM | NOTSET | FULL STOP | FULLCTI]

ETF.view

ETR.Base <address>

ETR.CATUBase <address>

ETR.Name <string>

ETR.NoFlush [ON | OFF]

ETR.RESet

ETR.Size <size>

ETR.STackMode [NotAvailbale | TRGETM | FULLTIDRM | NOTSET | FULL STOP | FULLCTI]

ETR.view

ETS.ATBSource < source >

ETS.Base <address>

ETS.Name <string>

ETS.NoFlush [ON | OFF]

ETS.RESet

ETS.Size <size>

ETS.STackMode [NotAvailbale | TRGETM | FULLTIDRM | NOTSET | FULL STOP | FULLCTI]

**ETS.view**

FUNNEL.Base < address>

FUNNEL.RESet

FUNNEL.Name <string>

FUNNEL.PROGrammable [ON | OFF]

**FUNNEL.view**

©1989-2023 Lauterbach ARC Debugger and Trace | 20

<parameter>: (Components

cont.)

REP.ATBSource < source > REP.Base <address> REP.Name <string>

**REP.RESet REP.view**

TPIU.Base <address> TPIU.Name <string>

TPIU.RESet

TPIU.Type [CoreSight | Generic]

TPIU\_view

<sub cmd>: (misc)

**DEBUGTIMESCALE** < multiplier> ADDRTICYCLES <dr> <ir>

The **SYStem.CONFIG** commands inform the debugger about the available on-chip debug and trace components and how to access them.

Some commands need a certain CPU type selection (SYStem.CPU <type>) for Lauterbach debug hardware to become active.

Ideally you can select with SYStem.CPU the chip you are using which causes all setup you need and you do not need any further SYStem.CONFIG command.

The SYStem.CONFIG command information shall be provided after the SYStem.CPU command, which might be a precondition to enter certain SYStem.CONFIG commands, and before you start up the debug session e.g. by SYStem.Up.

## <parameters> describing the "DebugPort"

CJTAGFLAGS <flags> Activates workarounds for incomplete or buggy cJTAG (IEEE

1149.7) implementations.

Bit 0: Disable scanning of cJTAG ID (TCA-scanning).

Bit 1: Target has no "keeper". Use TRACE32 pseudo keeper.

Bit 2: Inverted meaning of SREDGE register. Bit 3: Old command opcodes (cJTAG < 1.14).

Bit 4: APFC unlock required.

Bit 5: OAC required

Default: 0

CJTAGTCA <value> Selects the TCA (TAP Controller Address) to address a device in a

cJTAG (IEEE 1149.7) Star-2 configuration. The Star-2

configuration requires a unique TCA for each device on the debug

port.

#### CONNECTOR [MIPI34 | MIPI20T]

Specifies the connector "MIPI34" or "MIPI20T" on the target. This is mainly needed in order to notify the trace pin location.

This command is only available if the used Lauterbach debug cable supports different pin-outs. E.g. if a CombiProbe is used with a MIPI34 whisker.

Default: MIPI34.

#### CORE <core> <chip>

The command helps to identify cores which have debug and trace resources which are commonly used by different cores. The command might be required in a multicore environment if you use multiple debugger instances (multiple TRACE32 PowerView GUIs) to simultaneously debug different cores on the same target system over the same PowerDebug.

All core which share the same debug resources should have the same <chip> number.

E.g.: If you SoC contains an ARConnect unit for inter-core communication and cross-triggering, all cores, which arc connected to the same ARConnect should have the same <chip> number. (Otherwise truly synchronous start and stop of the cores wouldn't work)

This are the default settings of the command:

1st TRACE32 PowerView GUI: <core>=1 <chip>=1 2nd TRACE32 PowerView GUI: <core>=1 <chip>=2

n-th TRACE32 PowerView GUI: <core>=1 <chip>=n This means that by default the cores are handled as unrelated.

#### CoreNumber < number>

Number of cores to be considered in an SMP (symmetric multiprocessing) debug session.

#### DEBUGPORT [DebugCableA | DebugCableB]

In case you're using a Lauterbach CombiProbe with two MIPI34 whiskers, this command allows to select the whisker cable, which should be used by the current TRACE32 PowerView GUI.

#### DEBUGPORTTYPE [JTAG | SWD | CJTAG]

It specifies the used debug port type "JTAG", "SWD", "CJTAG", "CJTAG-SWD". It assumes the selected type is supported by the target.

- JTAG: Standard 5- or 4-pin JTAG (IEEE 1149.1)

- **CJTAG**: Compact 2-wire-JTAG (IEEE 1149.7)

- SWD: ARM Serial Wire Debug (requires that the ARC debug logic is connected to a CoreSight DAP inside the target SoC)

- CJTAGSWD: CJTAG in a mixed SWD/cJTAG configuration.

Default: JTAG

#### SWDP [ON | OFF]

With this command you can change from the normal JTAG communication to Serial Wire Debug. SWD (Serial Wire Debug) uses just two signals instead of five. It works only if your target SoC contains a CoreSight DAP and the ARC core debug register are connected to that DAP (via APB or JTAG-AP)

If SYStem.CONFIG.DEBUGPORTTYPE is set to CJTAGSWD, this command selects if cJTAG or SWD should be used.

Default: OFF.

#### Slave [ON | OFF]

(default: OFF) If more than one debugger share the same JTAG port, all except one must have this option active. Only one debugger - the "master" - is allowed to control the signals nTRST and nSRST (nRESET).

Default: OFF for the first TRACE32 PowerView GUI connected a PowerDebug, ON for every further TRACE32 PowerView GUI connected to the same PowerDebug for AMP multicore debugging.

#### **SWDPIdleHigh** [ON | OFF]

Keep SWDIO line high when idle. Only for Serialwire Debug mode. Usually the debugger will pull the SWDIO data line low, when no operation is in progress, so while the clock on the SWCLK line is stopped (kept low).

You can configure the debugger to pull the SWDIO data line high, when no operation is in progress by using SYStem.CONFIG SWDPIdleHigh ON

Default: OFF.

#### SWDPTargetSel <value>

Device address in case of a multidrop Serial Wire Debug Port. Default: OFF.

#### TriState [ON | OFF]

TriState has to be set to ON if several debug cables are connected to a common JTAG port. TAPState and TCKLevel define the TAP state and TCK level which is selected when the debugger switches to tristate mode. Please note: nTRST must have a pull-up resistor on the target, TCK can have a pull-up or pull-down resistor, other trigger inputs need to be kept in inactive state. (Pull-down resistor on TCK is strongly recommended!)

Default: OFF.

#### MADI

Some chips with multiple ARC cores use the so-called Multiple ARCtangent Processor Debug Interface (MADI). MADI is a multiplexer which allows you to debug several ARC cores via one JTAG TAP.

While you select the TAP with IRPRE, IRPOST, DRPRE, DRPOST the MADI options tells the debugger which core connected to the MADI-TAP you want to debug.

Setting MADI to OFF means you don't have a MADI IP between your TAP and your core.

If your target system does not have MADI, MADI is set automatically to OFF.

## <parameters> describing the "JTAG" scan chain and signal behavior

With a JTAG interface you can access a Test Access Port controller (TAP) which has implemented a state machine to provide a mechanism to read and write data to an Instruction Register (IR) and a Data Register (DR) in the TAP. The JTAG interface will be controlled by 5 signals:

- nTRST (reset)

- TCK (clock)

- TMS (state machine control)

- TDI (data input)

- TDO (data output)

Multiple TAPs can be controlled by one JTAG interface by daisy-chaining the TAPs (serial connection). If you want to talk to one TAP in the chain, you need to send a BYPASS pattern (all ones) to all other TAPs. For this case the debugger needs to know the position of the TAP it wants to talk to.

To tell the debugger the exact position of your core's Test Access Port controller (TAP) within a JTAG daisychain you'll require the commands IRPRE, IRPOST, DRPRE, and DRPOST.

Most ARC cores are directly connected to JTAG Test Access Port controller (TAP), which is accessible directly to the debugger via JTAG. However, in case you're ARC core is debugged via a CoreSight DAP you'll need DAPDRPRE/POST and DAPIRPRE/POST below instead.

| DRPRE <bits></bits> | (default: 0) < number > of TAPs in the JTAG chain between the     |

|---------------------|-------------------------------------------------------------------|

|                     | core of interest and the TDO signal of the debugger. If each core |

|                     | in the system contributes only one TAP to the JTAG chain,         |

|                     | DRPRE is the number of cores between the core of interest and     |

|                     | the TDO signal of the debugger.                                   |

(default: 0) < number > of TAPs in the JTAG chain between the TDI signal of the debugger and the core of interest. If each core in the system contributes only one TAP to the JTAG chain, DRPOST is the number of cores between the TDI signal of the debugger and the core of interest.

(default: 0) < number > of instruction register bits in the JTAG chain between the core of interest and the TDO signal of the debugger. This is the sum of the instruction register length of all TAPs between the core of interest and the TDO signal of the debugger.

(default: 0) < number > of instruction register bits in the JTAG chain between the TDI signal and the core of interest. This is the sum of the instruction register lengths of all TAPs between the TDI signal of the debugger and the core of interest.

DRPOST <bits>

IRPRE <bits>

IRPOST <bits>

NOTE:

If you are not sure about your settings concerning IRPRE, IRPOST, DRPRE, and **DRPOST**, you can try to detect the settings automatically with the SYStem.DETECT.SHOWChain command.

If you JTAG daisy chain contains a CoreSight DAP and the DAP is accessible via JTAG the DAP's JTAG Test Access Port controller (TAP) may also be inside a JTAG daisy-chain. To tell the debugger the exact position DAP's TAP within the JTAG daisy-chain you'll require the commands DAPIRPRE, DAPIRPOST, DAPDRPRE, and DAPDRPOST. These settings are especially important if the CoreSight DAP is not just used to access memory, but also your ARC cores's debug registers are also accessed via the DAP.

DAPDRPOST <br/>

<br/>

bits> (default: 0) < number > of TAPs in the JTAG chain between the

DAP and the TDO signal of the debugger.

**DAPDRPRE** <br/>

<br/>

bits> (default: 0) < number > of TAPs in the JTAG chain between the

TDI signal of the debugger and the DAP.

DAPIRPOST <br/>

<br/>

bits> (default: 0) < number > of instruction register bits in the JTAG

> chain between the DAP and the TDO signal of the debugger. This is the sum of the instruction register length of all TAPs between the DAP and the TDO signal of the debugger.

**DAPIRPRE** <br/>

<br/>

bits> (default: 0) < number > of instruction register bits in the JTAG

> chain between the TDI signal and the DAP. This is the sum of the instruction register lengths of all TAPs between the TDI signal of

the debugger and the DAP.

Slave [ON | OFF]

If more than one debugger share the same JTAG port, all except one must have this option active. Only one debugger - the "master" - is allowed to control the signals nTRST and nSRST

(nRESET).

Default: OFF for the first TRACE32 PowerView GUI connected a PowerDebug, ON for every further TRACE32 PowerView GUI connected to the same PowerDebug for AMP multicore

debugging.

TriState [ON | OFF]

TriState has to be set to ON if several debug cables are connected to a common JTAG port. TAPState and TCKLevel define the TAP state and TCK level which is selected when the debugger switches to tristate mode. Please note: nTRST must have a pull-up resistor on the target, TCK can have a pull-up or pull-down resistor, other trigger inputs need to be kept in inactive state. (Pull-down resistor

on TCK is strongly recommended!)

Default: OFF.

TCKLevel </evel>

Level of TCK signal when all debuggers are tristated. Normally defined by a pull-up or pull-down resistor on the target. (Pulldown resistor on TCK is strongly recommended!)

Default: 0.

TAPState <state>

This is the state of the TAP controller when the debugger switches to tristate mode. All states of the JTAG TAP controller are selectable.

0 Exit2-DR 1 Exit1-DR 2 Shift-DR 3 Pause-DR 4 Select-IR-Scan 5 Update-DR 6 Capture-DR 7 Select-DR-Scan

8 Exit2-IR 9 Exit1-IR 10 Shift-IR 11 Pause-IR 12 Run-Test/Idle 13 Update-IR 14 Capture-IR 15 Test-Logic-Reset

Default: 7 = Select-DR-Scan.

### MultiTap

MULTITAP [NONE | **PrimaryTAP** <args>] For command descriptions, see SYStem.CONFIG.MULTITAP.

**MULTITAP**

JtagSEQuence.<sub\_cmd>

For command descriptions, see

SYStem.CONFIG.MULTITAP JtagSEQuence.

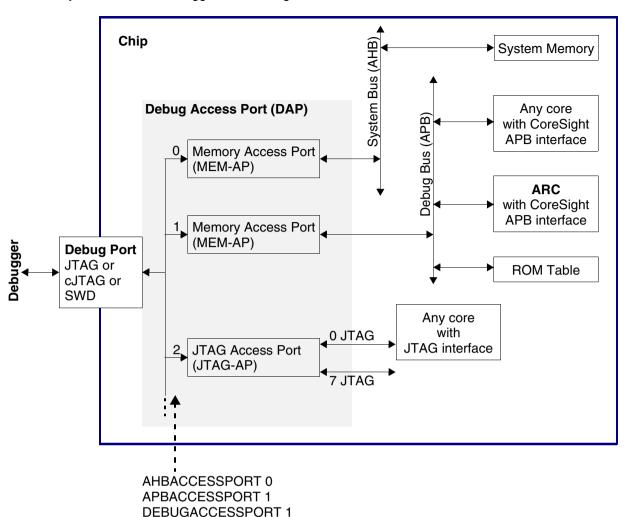

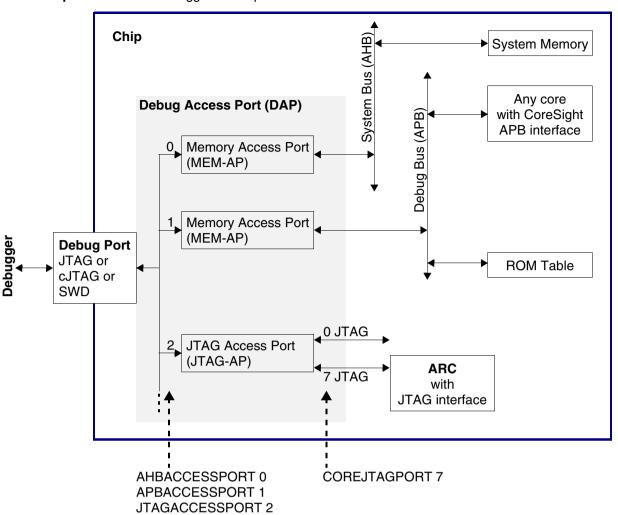

A Debug Access Port (DAP) is a CoreSight module from ARM which provides access via its debug port (JTAG, cJTAG, SWD) to:

- Memory busses (AHB, APB, AXI). This is especially important if the on-chip debug register needs to be accessed this way. You can access the memory buses by using certain access classes with the debugger commands: "AHB:", "APB:", "AXI:. The interface to these buses is called Memory Access Port (MEM-AP).

- The debug registers of some cores are accessible via such a memory bus (mostly APB).

- Chip-internal JTAG interfaces. This is important if the core you intend to debug is connected to such an internal JTAG interface. The module controlling these JTAG interfaces is called JTAG Access Port (JTAG-AP). Each JTAG-AP can control up to 8 internal JTAG interfaces. A port number between 0 and 7 denotes the JTAG interfaces to be addressed

The following **SYStem.CONFIG** commands configure the port-number for the memory busses:

| AHBACCESSPORT <port></port>   | DAP access port number (0-255) which shall be used for "AHB:" access class. Default: <port>=0.</port>                                                              |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APBACCESSPORT <port></port>   | DAP access port number (0-255) which shall be used for "APB:" access class. Default: <pre><pre><pre><pre><pre><pre></pre></pre></pre></pre></pre></pre>            |

| AXIACCESSPORT <port></port>   | DAP access port number (0-255) which shall be used for "AXI:" access class. Default: port not available                                                            |

| DEBUGACCESSPORT <port></port> | DAP access port number (0-255) where the debug register can be found (typically on APB). Used for "DAP:" access class. Default: <pre><pre>cport&gt;=1</pre>.</pre> |

The following SYStem.CONFIG commands are required if your ARC core is connected to a chip-internal JTAG interface, which is controlled via the DAP:.

| JTAGACCESSPORT <port></port> | DAP access port number (0-255) of the JTAG Access Port.                  |

|------------------------------|--------------------------------------------------------------------------|

| COREJTAGPORT <port></port>   | JTAG-AP port number (0-7) connected to the core which shall be debugged. |

©1989-2023 Lauterbach ARC Debugger and Trace | 28

Example 1: ARC core debugged via CoreSight APB interface

**Example 2**: ARC core debugged via chip-internal JTAG interface controlled via the DAP:

## <parameters> describing debug and trace "Components"

On the **COmponents** tab of the **SYStem.CONFIG.state** window, you can comfortably add the debug and trace components your chip includes and which you intend to use with the debugger's help.

©1989-2023 Lauterbach ARC Debugger and Trace

30

Each configuration can be done by a command in a script file as well. Then you do not need to enter everything again on the next debug session. If you press the button with the three dots you get the corresponding command in the command line where you can view and maybe copy it into a script file.

... .ATBSource <source>

Specify for components collecting trace information from where the trace data are coming from. This way you inform the debugger about the interconnection of different trace components on a common trace bus.

You need to specify the "... .Base <address>" or other attributes that define the amount of existing peripheral modules before you can describe the interconnection by "... .ATBSource <source>".

A CoreSight trace FUNNEL has eight input ports (port 0-7) to combine the data of various trace sources to a common trace stream. Therefore you can enter instead of a single source a list of sources and input port numbers.

... .Base <address>

This command informs the debugger about the start address of the register block of the component. And this way it notifies the existence of the component. An on-chip debug and trace component typically provides a control register block which needs to be accessed by the debugger to control this component.

Name

The name is a freely configurable identifier to describe how many instances exists in a target systems chip. TRACE32 PowerView GUI shares with other opened PowerView GUIs settings and the state of components identified by the same name and component type. Components using different names are not shared. Other attributes as the address or the type are used when no name is configured.

#### **Example 1: Shared None-Programmable Funnel:**

PowerView1:

SYStem.CONFIG.FUNNEL.PROGramable OFF SYStem.CONFIG.FUNNEL.Name "shared-funnel-1" PowerView2:

SYStem.CONFIG.FUNNEL.PROGramable OFF SYStem.CONFIG.FUNNEL.Name "shared-funnel-1" SYStem.CONFIG.Core 2. 1.; merge configuration to describe a target system with one chip containing a single noneprogrammable FUNNEL.

©1989-2023 Lauterbach

#### **Example 2: Cluster ETFs:**

1. Configures the ETF base address and access for each core SYStem.CONFIG.ETF.Base DAP:0x80001000 \

APB:0x80001000 DAP:0x80001000 APB:0x80001000

2. Tells the system the core 1 and 3 share cluster-etf-1 and core 2 and 4 share cluster-etf-2 despite using the same address for all **ETFs**

SYStem.CONFIG.ETF.Name "cluster-etf-1" "cluster-etf-2" \ "cluster-etf-1" "cluster-etf-2"

#### .... .NoFlush [ON | OFF]

Deactivates a component flush request at the end of the trace recording. This is a workaround for a bug on a certain chip. You will loose trace data at the end of the recording. Don't use it if not needed. Default: OFF.

.....RESet

Undo the configuration for this component. This does not cause a physical reset for the component on the chip.

... .Size <size>

Specifies the size of the component. The component size can normally be read out by the debugger. Therefore this command is only needed if this can not be done for any reason.

#### ....STackMode [NotAvailbale | TRGETM | FULLTIDRM | NOTSET | FULLSTOP | **FULLCTI**

Specifies the which method is used to implement the Stack mode of the on-chip trace.

NotAvailable: stack mode is not available for this on-chip trace. TRGETM: the trigger delay counter of the onchip-trace is used. It starts by a trigger signal that must be provided by a trace source. Usually those events are routed through one or more CTIs to the on-chip trace.

FULLTIDRM: trigger mechanism for TI devices.

**NOTSET**: the method is derived by other GUIs or hardware. detection.

**FULLSTOP**: on-chip trace stack mode by implementation. FULLCTI: on-chip trace provides a trigger signal that is routed back to on-chip trace over a CTI.

... .view

Opens a window showing the current configuration of the component.

ETR.CATUBase < address>

Base address of the CoreSight Address Translation Unit (CATU).

FUNNEL.Name <string>

It is possible that different funnels have the same address for their control register block. This assumes they are on different buses and for different cores. In this case it is needed to give the funnel different names to differentiate them

32

@1989-2023 Lauterbach ARC Debugger and Trace

#### **FUNNEL.PROGrammable** [ON | OFF]

Default is ON. If set to ON the peripheral is controlled by TRACE32 in order to route ATB trace data through the ATB bus network. If PROGrammable is configured to value OFF then TRACE32 will not access the FUNNEL registers and the base address doesn't need to be configured. This can be useful for FUNNELs that don't have registers or when those registers are read-only. TRACE32 need still be aware of the connected ATB trace sources and sink in order to know the ATB topology. To build a complete topology across multiple instances of PowerView the property Name should be set at all instances to a chip wide unique identifier.

#### TPIU.Type [CoreSight | Generic1

Selects the type of the Trace Port Interface Unit (TPIU).

CoreSight: Default. CoreSight TPIU. TPIU control register located at TPIU.Base <address> will be handled by the debugger.

Generic: Proprietary TPIU. TPIU control register will not be handled by the debugger.

#### Components and Available Commands

See the description of the commands above. Please note that there is a common description for ... .ATBSource, ... .Base, , ... .RESet, ... .TraceID.

#### COREDEBUG.Base < address> **COREDEBUG.RESet**

Core Debug Register - ARM debug register, e.g. on Cortex-A/R

Some cores do not have a fix location for their debug register used to control the core. In this case it is essential to specify its location before you can connect by e.g. SYStem.Up.

ETB.Base <address> ETB.Name <string> ETB.NoFlush [ON | OFF] ETB.RESet

ETB.Size <size>

Embedded Trace Buffer (ETB) - ARM CoreSight module

Enables trace to be stored in a dedicated SRAM. The trace data will be read out through the debug port after the capturing has finished.

ETF.Base <address> ETF.Name <string> ETF.RESet

Embedded Trace FIFO (ETF) - ARM CoreSight module

On-chip trace buffer used to lower the trace bandwidth peaks.

ETR.Base <address> ETR.Name <string> ETR.RESet

Embedded Trace Router (ETR) - ARM CoreSight module

Enables trace to be routed over an AXI bus to system memory or to any other AXI slave.

ETS.ATBSource < source > ETS.Base <address> ETS.Name <string> ETS.RESet

Embedded Trace Streamer (ETS) - ARM CoreSight module

FUNNEL.Base <address> FUNNEL.Name <string> FUNNEL.PROGrammable [ON | OFF] FUNNEL.RESet

CoreSight Trace Funnel (CSTF) - ARM CoreSight module

Combines multiple trace sources onto a single trace bus (ATB = AMBA Trace Bus)

REP.ATBSource <sourcelist> REP.Base <address> REP.Name < string> **REP.RESet**

CoreSight Replicator - ARM CoreSight module

This command group is used to configure ARM Coresight Replicators with programming interface. After the Replicator(s) have been defined by the base address and optional names the ATB sources REPlicatorA and REPlicatorB can be used from other ATB sinks to connect to output A or B to the Replicator.

TPIU.Base <address> TPIU.Name <string> TPIU.RESet

Trace Port Interface Unit (TPIU) - ARM CoreSight module

Trace sink sending the trace off-chip on a parallel trace port (chip pins).

@1989-2023 Lauterbach

#### **Multicore with JTAG Daisy Chain**

```

TDI --|-> Core A ---> Core B --|--|-> ARC ---> Core D -|--> TDO

+----+ +-----+

Chip2

Chip1

```

#### Instruction register length of

- Core A: 3 bit

- Core B: 5 bit

- Core D: 6 bit

```

SYStem.CONFIG.IRPRE 6

; IR Core D

SYStem.CONFIG.IRPOST 8

; IR Core A + B

SYStem.CONFIG.DRPRE 1

; DR Core D

SYStem.CONFIG.DRPOST 2

; DR Core A + B

SYStem.CONFIG.CORE 1. 2.

; Core 1 in Chip 2

SYStem.Up

```

#### SMP multicore debugging of a quad-core ARC-HS

Setup for a ARC-HS quad core, which should debugged in SMP mode, which means that all 4 core are debugged via the same TRACE32 PowerView GUI. SMP is the right mode if all cores share the same memory and task. E.g. when Linux is running on the ARC quad core cluster.

In this example all ARC cores of the quad-core cluster have a separate JTAG-TAP, which is the most common configuration.

```

SYStem.CPU ARC-HS

SYStem.CONFIG CoreNumber 4

SYStem.CONFIG IRPRE 12.

8.

4.

0.

SYStem.CONFIG DRPRE

3.

2. 1.

0.

SYStem.CONFIG IRPOST 0. 8. 4.

12.

SYStem.CONFIG DRPOST 0. 1.

3.

CORE.ASSIGN 1 2 3 4

SYStem.Up

```

#### Multicore with Multiple ARCtangent Processor Debug Interface (MADI)

```

SYStem.CONFIG MADI 2

; Debug 3rd core attached to MADI

SYStem.Up

```

## SYStem.CPU

Select CPU type

Format: SYStem.CPU <cpu>

AUTO | <cpu>:

> ARCtangent-A4 ARCtangent-A5 | ARC600 | ARC601

**ARC700**

ARC-EM | ARC-EM-1r0 |

ARC-HS |

ARC-EV6x | ARC-EV7x | ARC-VPX5 |

Default: AUTO.

Selects the processor type.

AUTO reads out the IDENTITY auxiliary register after a SYStem.Up or SYStem.Mode Attach, and sets the system CPU to the detected core accordingly.

Format: SYStem.JtaqClock [<clockmode>] <frequency>

<clockmode>: RTCK | ARTCK | CTCK | CRTCK

(<clockmode> only available if an ARM debug cable (e.g. LA-3750) is used.)

<frequency>: 6 kHz ... 80 MHz

1250000. | 2500000. | 5000000. | 10000000. (on obsolete ICD hardware)

(<frequency> is optional if <clockmode> is set to RTCK)

Default frequency: 10 MHz.

Selects the JTAG port frequency (TCK) used by the debugger to communicate with the processor. The frequency affects e.g. the download speed. It could be required to reduce the JTAG frequency if there are buffers, additional loads or high capacities on the JTAG lines or if VTREF is very low. A very high frequency will not work on all systems and will result in an erroneous data transfer. Therefore we recommend to use the default setting if possible.

<frequency> The debugger cannot select all frequencies accurately. It chooses the

next possible frequency and displays the real value in the SYStem.state

window.

Besides a decimal number like "100000." short forms like "10kHz" or "15MHz" can also be used. The short forms imply a decimal value.

although no "." is used.

**RTCK** The JTAG clock is controlled by the RTCK signal (Returned TCK).

> On some processor derivatives there is the need to synchronize the processor clock and the JTAG clock. In this case RTCK shall be selected. Synchronization is maintained, because the debugger does not progress

to the next TCK edge until after an RTCK edge is received.

In case you have a processor derivative requiring a synchronization of the processor clock and the JTAG clock, but your target does not provide an RTCK signal, you need to select a fix JTAG clock below 2/3 of the

processor clock.

When RTCK is selected, the frequency depends on the processor clock and on the propagation delays. The maximum reachable frequency is

about 16 MHz.

Example: SYStem.JtagClock RTCK

#### **ARTCK**

Accelerated method to control the JTAG clock by the RTCK signal (Accelerated Returned TCK).

Theoretically RTCK mode allows frequencies up to 2/3 of the processor clock.

For designs using a very low processor clock we offer a different mode (ARTCK) which might not work on all target systems. In ARTCK mode the debugger uses a fixed JTAG frequency for TCK, independent of the RTCK signal. TDI and TMS will be delayed by 1/2 TCK clock cycle. TDO will be sampled with RTCK

#### **CTCK**

With this option higher JTAG speeds can be reached.

The TDO signal will be sampled by a signal which derives from TCK, but which is timely compensated regarding the debugger-internal driver propagation delays (Compensation by TCK). This feature can be used with a debug cable versions 3b or newer. If it is selected, although the debug cable is not suitable, a fix JTAG clock will be selected instead (minimum of 10 MHz and selected clock).

#### CRTCK

With this option higher JTAG speeds can be reached, if your target provides RTCK.

The TDO signal will be sampled by the RTCK signal. This compensates the debugger-internal driver propagation delays, the delays on the cable and on the target (Compensation by RTCK). This feature requires that the target provides an RTCK signal. In contrast to the **RTCK** option, the TCK is always output with the selected, fixed frequency.

The modes RTCK, ARTCK, CRTCK can only be used if the target provides an RTCK signal.

Furthermore the modes are only available with the 20-pin Debug Cable LA-3750 (or LA-3750A in an ARM Debug Cable).

Format: SYStem.LOCK [ON | OFF]

Default: OFF.

If the system is locked, no access to the debug port will be performed by the debugger. While locked, the debug connector of the debugger is tristated. The main intention of the SYStem.LOCK command is to give debug access to another tool.

The process can also be automated, see **SYStem.CONFIG TriState**.

It must be ensured that the state of the JTAG state machine remains unchanged while the system is locked. To ensure correct hand-over, the options SYStem.CONFIG TAPState and SYStem.CONFIG TCKLevel must be set properly. They define the TAP state and TCK level which is selected when the debugger switches to tristate mode. Please note: nTRST must have a pull-up resistor on the target.

### SYStem.MemAccess

Real-time memory access (non-intrusive)

Format: SYStem.MemAccess Enable | Denied | StopAndGo | <cpu specific>

SYStem.ACCESS (deprecated)

**Enable** Real-time memory access during program execution to target is enabled.

CPU (deprecated)

**Denied** Real-time memory access during program execution to target is disabled.

StopAndGo Temporarily halts the core(s) to perform the memory access. Each stop

takes some time depending on the speed of the JTAG port, the number of the assigned cores, and the operations that should be performed.

For more information, see below.

This option declares if an **non-intrusive** memory access can take place while the CPU is executing code. Although the CPU is not halted, run-time memory access creates an additional load on the processor's internal data bus

If SYStem.MemAccess is not Denied, it is possible to read from memory, to write to memory and to set software breakpoints while the CPU is executing the program.

If specific windows that display memory or variables should be updated while the program is running, select the memory class prefix **E**: or the format option **%E**.

Data.dump ED:0x100 Data.List EP:main Var. View %E first

Format: SYStem.Mode < mode>

SYStem.Attach (alias for SYStem.Mode Attach)

SYStem.Down (alias for SYStem.Mode Down)

SYStem.Up (alias for SYStem.Mode Up)

<mode>: Down

NoDebug Attach Up Go Prepare

**Down** The debug adapter gets tristated.

The state of the CPU remains unchanged. Debug mode is not active. In this mode the target behaves as if the debugger is not connected.

If SYStem.Option.EnReset.ON is set to ON and SYStem.CONFIG.Slave is set to OFF the debugger will drive a low-active reset pulse on the

nRESET (nSRST) on the JTAG connector.

**NoDebug** The debug adapter gets tristated.

The state of the CPU remains unchanged. Debug mode is not active. In this mode the target behaves as if the debugger is not connected.

Attach Initializes the debug interface and connects to core while program

remains running.

After this command the user program can be stopped with the break

command or by any other break condition (e.g a breakpoints).

**Up** Initializes the debug interface, enters debug mode, stops the core and

initializes several registers to their reset value. The debugger sets the

program counter to the reset address of the core.

If SYStem.Option.EnReset.ON is set to ON and SYStem.CONFIG.Slave

is set to **OFF** the debugger will drive a low-active reset pulse on the

nRESET (nSRST) on the JTAG connector.

**Go** Start code execution from reset vector.

Actually the debugger performs the same actions than on

SYStem.Mode.Up followed by Go.direct.

#### Allow memory access without checking the go-stated of the core. **Prepare**

On SoCs with CoreSight DAP the debugger connects to the DAP and allows accesses to the APB, AHB and/or AXI bus - without communicating with the ARC core.

On SoCs with direct JTAG connection to the ARC core, memory can be accessed via the ARC core in prepare-mode.

#### StandBy Not available for ARC.

(This mode is used to start debugging from power-on. The debugger will wait until power-on is detected, then initialize the debug interface and connect to core.)

| NOTE: |

|-------|

|-------|

Format: SYStem.Option <option> <value>

Set target-specific options, e.g. SYStem.Option.Endianness or SYStem.Option.IMASKHLL. See the description of the available options below.

## SYStem.Option.AHBHPROT

Select AHB-AP HPROT bits

Format:

SYStem.Option.AHBHPROT <value>

Default: 0

Selects the value used for the HPROT bits in the Control Status Word (CSW) of an AHB Access Port of a DAP, when using the AHB: memory class.

This option is only meaningful, if the chip contains a CoreSight DAP.

## SYStem.Option.AXIACEEnable

ACE enable flag of the AXI-AP

Format:

SYStem.Option.AXIACEEnable [ON | OFF]

Default: OFF.

Enables ACE transactions on the DAP AXI-AP, including barriers. This does only work if the debug logic of the target CPU implements coherent AXI accesses. Otherwise this option will be without effect.

This option is only meaningful, if the chip contains a CoreSight DAP.

Format: SYStem.Option.AXICACHEFLAGS <value>

<value>: **DeviceSYStem**

> **NonCacheableSYStem** ReadAllocateNonShareable ReadAllocateInnerShareable ReadAllocateOuterShareable WriteAllocateNonShareable WriteAllocateInnerShareable WriteAllocateOuterShareable ReadWriteAllocateNonShareable ReadWriteAllocateInnerShareable ReadWriteAllocateOuterShareable

Default: DeviceSYStem (=0x30: Domain=0x3, Cache=0x0)

This option configures the value used for the Cache and Domain bits in the Control Status Word (CSW[27:24]->Cache, CSW[14:13]->Domain) of an AXI Access Port of a DAP, when using the AXI: memory class.

The below offered selection options are all non-bufferable. Alternatively you can enter a <value>, where value[5:4] determines the Domain bits and value[3:0] the Cache bits.

| DeviceSYStem                    | =0x30: Domain=0x3, Cache=0x0 |

|---------------------------------|------------------------------|

| NonCacheableSYStem              | =0x32: Domain=0x3, Cache=0x2 |

| ReadAllocateNonShareable        | =0x06: Domain=0x0, Cache=0x6 |

| ReadAllocateInnerShareable      | =0x16: Domain=0x1, Cache=0x6 |

| ReadAllocateOuterShareable      | =0x26: Domain=0x2, Cache=0x6 |

| WriteAllocateNonShareable       | =0x0A: Domain=0x0, Cache=0xA |

| WriteAllocateInnerShareable     | =0x1A: Domain=0x1, Cache=0xA |

| WriteAllocateOuterShareable     | =0x2A: Domain=0x2, Cache=0xA |

| ReadWriteAllocateNonShareable   | =0x0E: Domain=0x0, Cache=0xE |

| ReadWriteAllocateInnerShareable | =0x1E: Domain=0x1, Cache=0xE |

| ReadWriteAllocateOuterShareable | =0x2E: Domain=0x2, Cache=0xE |

This option is only meaningful, if the chip contains a CoreSight DAP.

Format: SYStem.Option.AXIHPROT <value>

Default: 0

This option selects the value used for the HPROT bits in the Control Status Word (CSW) of an AXI Access Port of a DAP, when using the AXI: memory class.

This option is only meaningful, if the chip contains a CoreSight DAP.

### SYStem.Option.CorePowerDetection

Set methods to detect core power

SYStem.Option.CorePowerDetection < method> Format:

<method>: JtaqSEQuence <seq name> | none

Sets and configures methods to detect the power of a core.

The core power is detected when **SYStem.Mode Up** is active or is entered. If a core is not powered, the debugger stays in system mode "Up" but displays the state "running (no power)" in the TRACE32 state line.

At the moment only the method **JtagSEQuence** is available.

| JtagSEQuence<br><seq_name></seq_name> | Enables the detection of the core power via a specified JTAG sequence. The specified JTAG sequence is periodically executed by the debug driver.  You can create a JTAG sequence with the command JTAG.SEQuence.Create.  The debug driver assumes that the core is powered when the JTAG sequence returns zero in the variable Resulto.  In case of an SMP system, use the environment variable PhysicalCORE within your JTAG sequence. |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JtagSequence none                     | Disables the detection of the core power via a JTAG sequence.                                                                                                                                                                                                                                                                                                                                                                           |

#### Example:

```

SYStem.RESet; resets SYStem settings (unlocks all used JTAG sequences)

SYStem.CPU ARC-HS

; create JTAG sequence for power detection

JTAG.SEQuence.Delete myCorePowerCheck ; delete old sequence

JTAG.SEQuence.Create myCorePowerCheck ; create new sequence

JTAG.SEQuence.Add , PrePostRelative +4. -4. +1. -1.

JTAG.SEQuence.Add , RawShift

4. 0x03 0x00

JTAG.SEOuence.Add , ShiftIrAndExit

4.0x07

JTAG.SEOuence.Add , RawShift

4. 0x03 0x00

JTAG.SEQuence.Add , ShiftDrAndExit 16. 0x00 Result0

JTAG.SEQuence.Add , RawShift

2. 0 \times 01 0 \times 00

JTAG.SEQuence.Add , ASSIGN Result0 = ~ Result0 & 0x0001

; use the new JTAG sequence for detecting the core power

SYStem.Option.CorePowerDetection.JtagSEQuence myCorePowerCheck

; connect to all cores of the chip

SYStem.Mode Attach

```

Format: SYStem.Option.DAPDBGPWRUPREQ [ON | AlwaysON | OFF]

Default: ON.

This option controls the DBGPWRUPREQ bit of the CTRL/STAT register of the Debug Access Port (DAP) before and after the debug session. Debug power will always be requested by the debugger on a debug session start because debug power is mandatory for debugger operation.

ON Debug power is requested by the debugger on a debug session start, and

the control bit is set to 1.

The debug power is released at the end of the debug session, and the

control bit is set to 0.

**AlwaysON** Debug power is requested by the debugger on a debug session start, and

the control bit is set to 1.

The debug power is **not** released at the end of the debug session, and the

control bit is set to 0.

**OFF** Only for test purposes: Debug power is **not** requested and **not** checked by

the debugger. The control bit is set to 0.

#### Use case:

Imagine an AMP session consisting of at least of two TRACE32 PowerView GUIs, where one GUI is the master and all other GUIs are slaves. If the master GUI is closed first, it releases the debug power. As a result, a debug port fail error may be displayed in the remaining slave GUIs because they cannot access the debug interface anymore.

To keep the debug interface active, it is recommended that SYStem.Option.DAPDBGPWRUPREQ is set to AlwaysON.

This option is only meaningful, if the chip contains a CoreSight DAP.

Format: **SYStem.Option.DAPREMAP** {<address range> <address>}

The Debug Access Port (DAP) can be used for memory access during runtime. If the mapping on the DAP is different than the processor view, then this re-mapping command can be used

NOTE: Up to 16 <address range>/<address> pairs are possible. Each pair has to contain an address range followed by a single address.

This option is only meaningful, if the chip contains a CoreSight DAP.

# SYStem.Option.DAPSYSPWRUPREQ

Force system power in DAP

Format: SYStem.Option.DAPSYSPWRUPREQ [AlwaysON | ON | OFF]

Default: ON.

This option controls the SYSPWRUPREQ bit of the CTRL/STAT register of the Debug Access Port (DAP) during and after the debug session

System power is requested by the debugger on a debug session start, and **AlwaysON**

the control bit is set to 1.

The system power is **not** released at the end of the debug session, and the

control bit remains at 1.

ON System power is requested by the debugger on a debug session start, and

the control bit is set to 1.

The system power is released at the end of the debug session, and the

control bit is set to 0.

System power is not requested by the debugger on a debug session start, **OFF**

and the control bit is set to 0.

This option is only meaningful, if the chip contains a CoreSight DAP.

Format: SYStem.Option.DAPNOIRCHECK [ON | OFF]

Default: OFF.

Bug fix for derivatives which do not return the correct pattern on a DAP (Arm CoreSight Debug Access Port) instruction register (IR) scan. When activated, the returned pattern will not be checked by the debugger.

This option is only meaningful, if the chip contains a CoreSight DAP.

#### SYStem.Option.DCFLUSH Invalidate/flush data-cache for modified memory

SYStem.Option.DCFLUSH [ON | OFF] Format:

Default: ON.

If the target memory is modified via the debugger, this option ensures that the data cache (and the 2nd level cache (SLC) if available) gets invalidated before the target CPU is restarted. Furthermore, the data cache gets flushed when the CPU stops.

If the option is disabled, the debugger checks for every target memory access if the data is cached. If so the debugger reads the data from the cache on a read access or writes the data separately to both target memory and the cache on a write access.